## **RISC-V Processor Verification: Case Study**

### UNITED STATES

VIRTUAL | MARCH 1-4, 2021

**DVCon 2021**

A. Maymon, S. Harari **Nvidia Networking**

L. Moore, L. Lapides **Imperas Software Ltd.**  Imperas

© 2021 Imperas Software Ltd.

- RISC-V processor DV problem

- Verification flow overview

- RISC-V reference models

- Simple step-and-compare flow

- Complex step-and-compare flow

- Results

- Conclusion

- RISC-V processor DV problem

- Verification flow overview

- RISC-V reference models

- Simple step-and-compare flow

- Complex step-and-compare flow

- Results

- Conclusion

# **RISC-V Progression**

| 2010-2016 | Hardware                                                                             | ISA definition, test chips                                                       |

|-----------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|           | Software                                                                             | tests                                                                            |

| 2017-2018 | Hardware (RV32)                                                                      | Proof of concept SoCs; "minion" processors for power management, communications, |

|           | Software                                                                             | Bare metal software                                                              |

| 2019-2020 | Hardware (RV32, privilege modes, interrupts)                                         | IoT SoCs; MCUs                                                                   |

|           | Software                                                                             | RTOS, firmware                                                                   |

| 2021-     | Hardware (RV64, multi-hart CPUs, vectors, bit manipulation, hypervisors, Debug mode) | Application processors; AI SoCs                                                  |

|           | Software                                                                             | Linux, drivers; AI compilers                                                     |

Increasing hardware and software complexity requires use of best known methods for processor and SoC architecture, implementation, design verification, software development

# The RISC-V Processor Design Verification (DV) Problem

### • Arm processor IP

- ~ 10<sup>15</sup> verification cycles per processor (10,000 simulators running constantly for 1 year)

- Verification of interface between NoC and processor

- 1,000s of SoC designs successfully produced

- Similar stories for ARC, MIPS, Tensilica, ...

- RISC-V IP questions

- How well verified is an individual processor (from processor IP vendor, open source, self-built)?

- How well verified is interface between NoC and processor?

- How to deal with custom instructions?

- RISC-V processor DV problem

- Verification flow overview

- RISC-V reference models

- Simple step-and-compare flow

- Complex step-and-compare flow

- Results

- Conclusion

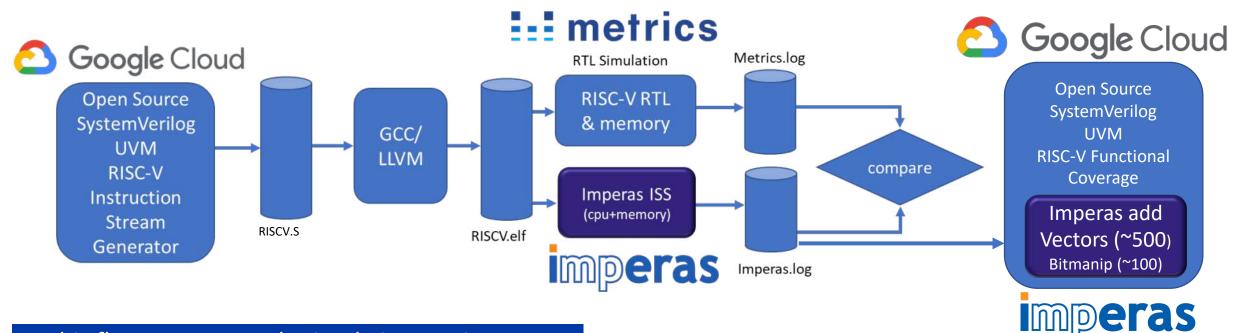

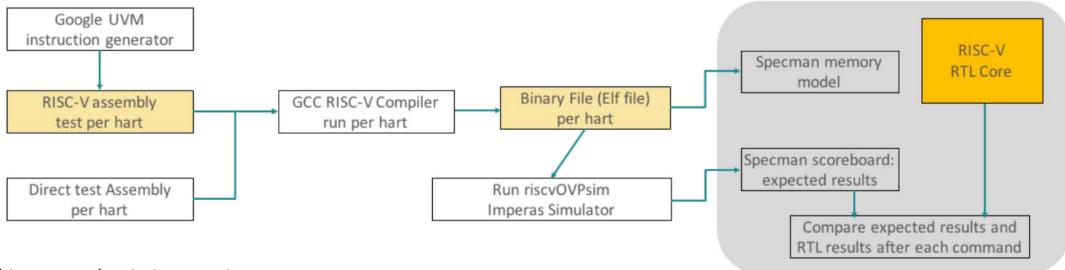

### Previous Work on RISC-V DV Uses Trace Comparison Flow

# mperas

- This flow supports only simple instruction test; cannot support asynchronous events including interrupts and Debug mode

- Trace compare is done post-simulation => easy to get started however inefficient use of simulation resources

- Google: open source riscv-dv instruction stream generator

- Metrics : SystemVerilog design + UVM simulator for RTL

- Imperas: model and simulation golden reference of RISC-V CPU

### Some Previous Work Used Step-and-Compare DV Flow

# mperas

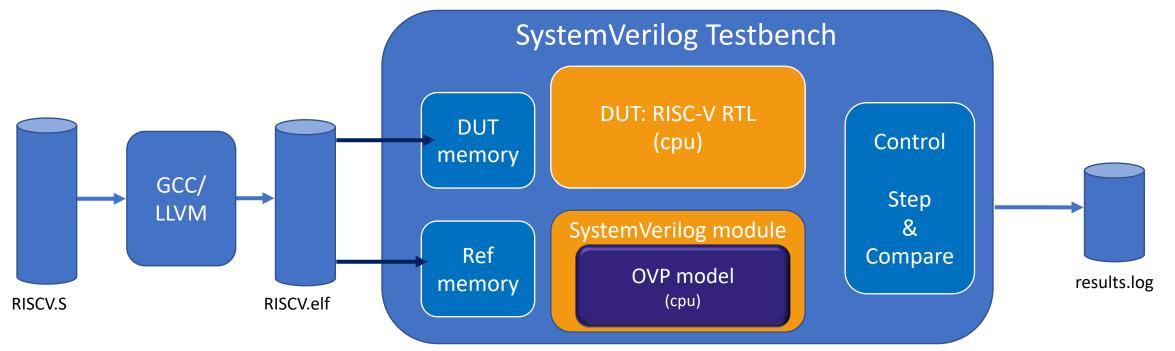

- OVP RISC-V model is encapsulated into SystemVerilog module

- Interfaces being: reset, clk, address bus, data bus, interrupts, registers, etc.,...

- Testbench loads .elf program into both memories, resets CPUs (RTL and OVP model)

- Steps CPUs, extracting data, and comparing

- There is no stored log file test log data is dynamic and requires two targets to be run and compared

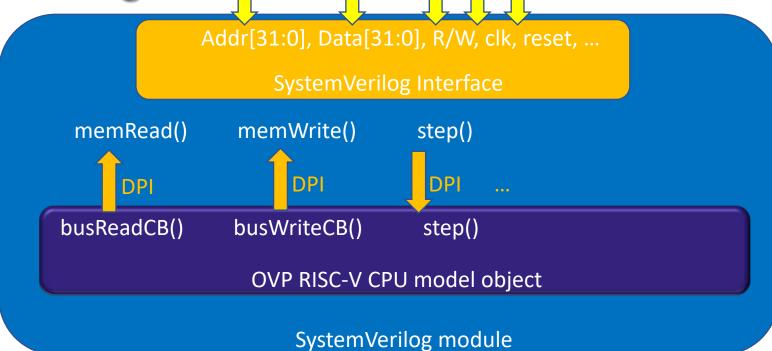

### Step-and-Compare Requires Encapsulation of the Reference Model in SystemVerilog

- The OVP model is a binary shared object of a RISC-V CPU model

- Encapsulated into a SystemVerilog module, using SystemVerilog DPI

- Instanced in SystemVerilog testbench like any module

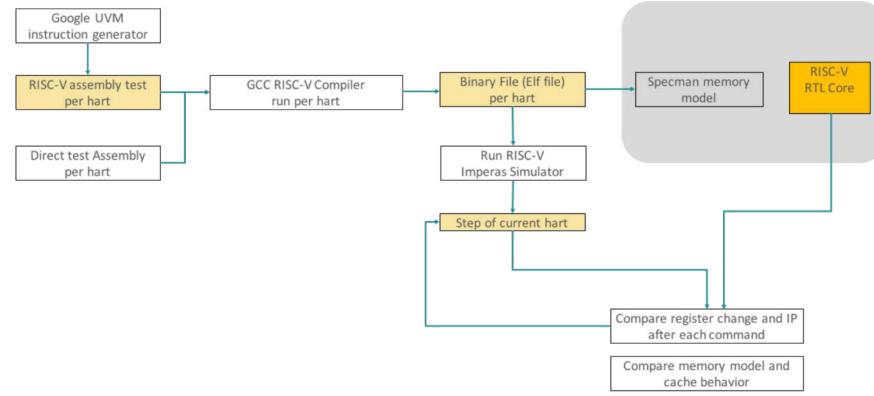

# Parallel Verification Flows Were Used for this Project

#### Simple Step-and-Compare

- Cadence Xcelium RTL simulator

- Cadence Specman verification environment

- Imperas riscvOVPsim instruction set simulator (RISC-V reference model and simulator combined)

- Used for verification of basic instruction functionality

- Complex Step-and-Compare

- Cadence Xcelium RTL simulator

- Cadence Specman verification environment

Imperas

- Open Virtual Platforms (OVP) RISC-V reference model, including support for custom instructions

- Imperas M\*DEV simulator

- Used for verification of asynchronous events, Debug mode, ...

#### Using parallel flows achieved optimal use of verification resources at the lowest cost.

- RISC-V processor DV problem

- Verification flow overview

- RISC-V reference models

- Simple step-and-compare flow

- Complex step-and-compare flow

- Results

- Conclusion

### RISC-V Reference Model Requirements

- Model the ISA, including all versions of the ratified spec, and stable unratified extensions

- Easily update and configure the model for the next project

- User-extendable for custom instructions, registers, interrupts/events, ...

- Model actual processor IP, e.g. Andes, SiFive, OpenHW CV32E40P, SweRV, ...

- Well-defined test process including coverage metrics

- Interface to other simulators, e.g. SystemVerilog, SystemC, Imperas virtual platform simulators

- Interface to software debug tools, e.g. GDB/Eclipse, Imperas MPD

- Interface to software analysis tools including access to processor internal state, etc.

- Interface to architecture exploration tools including extensibility to timing estimation

- Most RISC-V ISSs can meet one or two of these requirements

- Imperas models and simulators were built to satisfy these requirements, and matured through usage on non-RISC-V ISAs over the last 10+ years

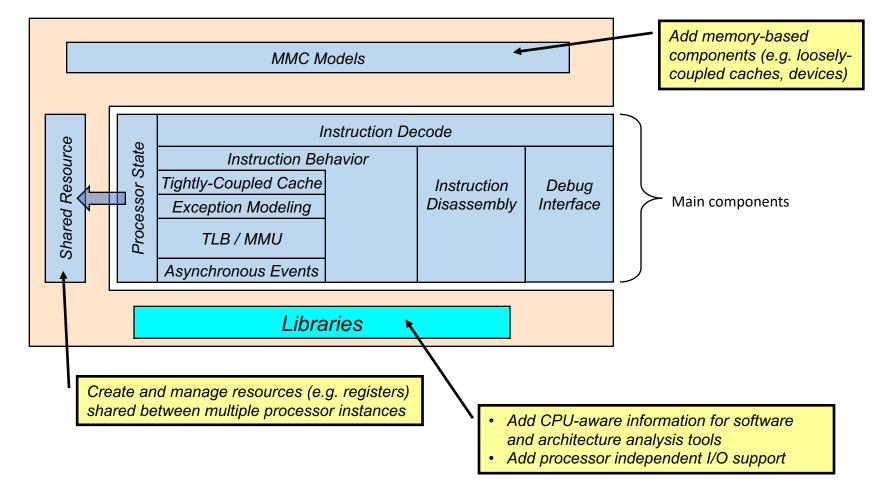

### Components of Open Virtual Platforms (OVP) Fast Processor Models

# mperas

OVP models are open source and free

- Models are built in C using OVP APIs; APIs are supported by OVPsim and Imperas simulators

- All models have both C and SystemC/TLM2 native interfaces

- Available under the Apache 2.0 open source license

- Require an Imperas simulator license to run

- 1 simulator license is all that is needed for multi-core and manycore platforms

#### http://www.ovpworld.org/info\_riscv

# OVP Library of RISC-V Fast Processor Models

- Existing Imperas Open Virtual Platforms (OVP) Fast Processor Models of ...

- Generic or envelope models of RV32/64 IMAFDCEVBHK M/S/U privilege modes

- Andes cores: A(X)25, N(X)25, N(X)25F, 27-series including NX27V, ...

- SiFive cores: SiFive Series 2, Series 3 (e.g. E31), Series 5 (e.g. E51, U54), Series 7

- OpenHW CV32E40P

- Custom features instructions, registers, interrupts/events easily added by user or by Imperas

- New features are added in side file so as not to perturb the verified model

- Custom instructions can be analyzed for effectiveness using instruction coverage, profiling tools

- Custom interrupts and events can be added to all spec flows and CSRs with priority and order consideration

- Models are built using Test Driven Development (TDD) methodology

- Tests are built at the same time as features are added

- Continuous Integration (CI) test flow used

- ~ 15,000 tests for models + simulator

- Mutation testing used to check quality of test suites

- Additional testing by processor IP vendors to validate models

Imperas

Open Virtual Platforms

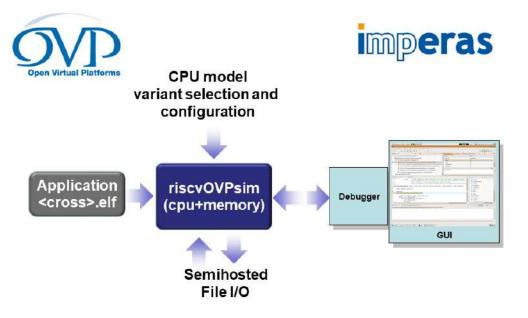

## RISC-V OVP Reference Model Configurability

Imperas riscvOVPsim Compliance Simulator

- Industrial quality, free ISS / reference model for instruction testing

- <u>https://www.ovpworld.org/info\_riscv</u>

- Model is built using Open Virtual Platforms (OVP) APIs

- Implements full RISC-V envelope

- Configurable for all features and spec versions

| Parameter Category    | Examples                                             |  |  |  |  |

|-----------------------|------------------------------------------------------|--|--|--|--|

| Specification version | Privilege spec version 1.10, 1.11, 1.12              |  |  |  |  |

|                       | Debug configuration spec version 0.13.4, 0.14        |  |  |  |  |

|                       | Bit manipulation spec version 0.90, 0.91, 0.92, 0.93 |  |  |  |  |

|                       | Vector spec version 0.71, 0.8, 0.9, 1.0              |  |  |  |  |

| Simple parameters     | MISA subsets 32/64 I, M, A, C, F, D, B, V, H, K,     |  |  |  |  |

|                       | Misaligned Code/Data access behavior                 |  |  |  |  |

|                       | CSR field/behavior configuration                     |  |  |  |  |

|                       | CLINT configuration                                  |  |  |  |  |

|                       | CLIC configuration                                   |  |  |  |  |

|                       | DEBUG configuration                                  |  |  |  |  |

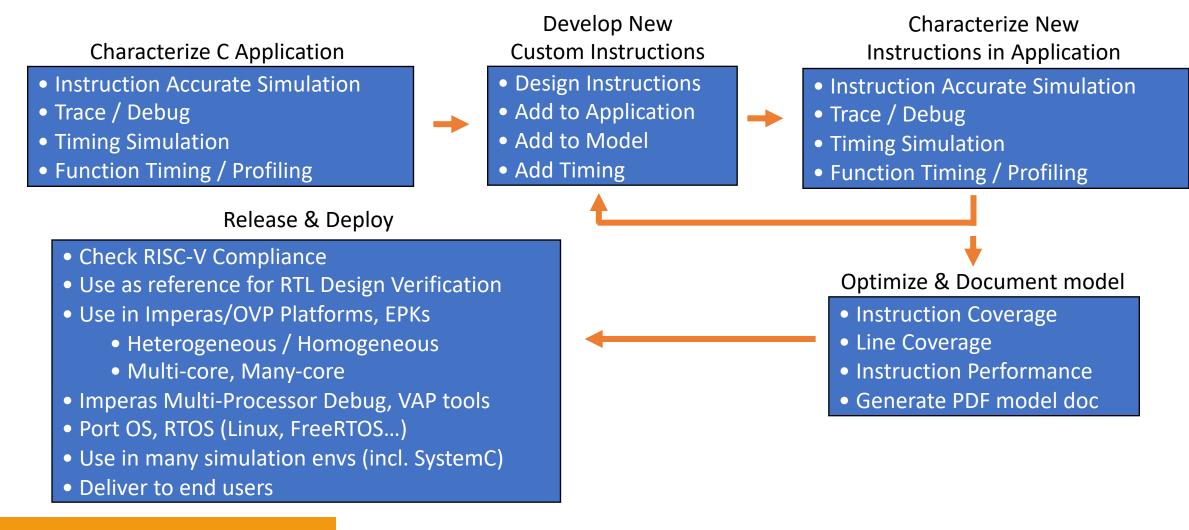

# Flow to Add Custom Instructions Imperas

#### Page 16

#### © 2021 Imperas Software Ltd.

### Adding Custom Instructions to Model Using Extension Library

# mperas

- Use standard Open Virtual Platforms (OVP) instruction modeling APIs to add new instructions (and optional state) as *new extension library*

- Easy to extend decode table, add efficient behavioral JIT code

- Compile and link model extension library

```

// Create the RISCV decode table

static vmidDecodeTableP createDecodeTable(void) {

vmidDecodeTableP table = vmidNewDecodeTable(RISCV INSTR BITS, RISCV EIT LAST);

// R-Type instruction in custom-0 encoding space:

// opcode [6:0] = 00 010 11

// funct3[14:12] = 0,1,2,3 (0R1-4)

// funct7[31:25] = 0800000

// rs1[19:15]

// rs2[24:20]

// rd[11:7]

// handle custom instruction

DECODE ENTRY(0, CHACHA200R2, "[0000000.....001.....001011]");

DECODE ENTRY(0, CHACHA200R3,

"[0000000.....010.....0001011[");

DECODE_ENTRY(0, CHACHA200R4, "|0000000.....011.....0001011|");

return table;

// Emit code implementing exchange instruction

static void emitChaCha20(

vmiProcessorP processor,

vmiosObjectP object,

Uns32

instruction.

Uns32

rotl

) {

// extract instruction fields

Uns32 rd = RD(instruction);

Uns32 rs1 = RS1(instruction);

Uns32 rs2 = RS2(instruction);

vmiReg reg rs1 = vmimtGetExtReg(processor, &object->rs1);

vmiReq req rs2 = vmimtGetExtReg(processor, &object->rs2);

vmiReg reg_tmp = vmimtGetExtTemp(processor, &object->tmp);

vmimtGetR(processor, RISCV_REG_BITS, reg_rs1, object->riscvRegs[rs1]);

vmimtGetR(processor, RISCV REG BITS, reg rs2, object->riscvRegs[rs2]);

vmimtBinopRRR(32, vmi_XOR, reg_tmp, reg_rs1, reg_rs2, 0);

vmimtBinopRC(32, vmi_ROL, reg_tmp, rotl, 0);

vmimtSetR(processor, RISCV REG BITS, object->riscvRegs[rd], reg tmp);

```

### Software Debug and Analysis Tools Automatically Work With the Custom Instructions

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | indow He | ib                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                      |             |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---|

| ) • 🗑 🖏 🖸 🕸 • O • 🏊 • 🙋 🗸 • 🔄 🗶 🕨 🖬 🔹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N 3. 3   | A 🕂 - 🕫 9.        | 🗢 🖓 👘 🖓 🖓 🖓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 🗢 🔹 🗢 Quick                                                                                                                                                                          | Access      | 4 |

| Debug 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 0      | (0)- Variables 23 | Breakpoints IIII Regi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | sters <table-of-contents> Modules</table-of-contents>                                                                                                                                |             |   |

| 1 🕨 🖬 🗰 🗱 🛛 🕱 🗷 🖓 🕂 🗮 🗌 💥 🎄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | () v     |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | E 🚧 🖯                                                                                                                                                                                | 11 H 🗞      | Ŷ |

| Platform Launch [Imperas - Connect to running simulator]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | Name              | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Value                                                                                                                                                                                |             |   |

| v im iss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 69- input         | unsigned int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2222400358                                                                                                                                                                           |             |   |

| 🗢 🍰 cpu0 [RV32IM riscv]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | 69- word          | unsigned int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2804990272                                                                                                                                                                           |             |   |

| v 🖗 ID #1 [cpu0] RV32IM riscv (Suspended : Breakpoint)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 60-res            | unsigned int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                    |             |   |

| processLine() at test_custom.c.5 0x10230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 9110020320        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                                                                                   |             |   |

| main() at test_custom.c:32 0x102e4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | -                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                      |             | E |

| 📓 mpd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                      |             | 6 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 0                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                                                                                   |             | D |

| test_custom.c 🛙 🗖 customChaCha20. 📑 riscv32.c 💽 _start() at 0x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ×1 *1    | 🖻 🗄 📴 Out         | line 🗤 Programmers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | View 🔤 Disassembly 🛙                                                                                                                                                                 | -           |   |

| <pre>// Custom instruction test for Chacha20 #include <stdio.h></stdio.h></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                   | Enter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ocation here 🗸 👔 🕅                                                                                                                                                                   |             | ~ |

| <pre>unsigned int processLine(unsigned int input, unsigned int word){     unsigned int res = input;     asm _volatile_("mv x10, %0" :: "r"(res));     asm _volatile_("mv x11, %0" :: "r"(word));     asm _volatile_(".word 0x00850508\n" :: "x10"); // 0R1     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R2     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R3     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R4     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R3     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R4     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R4     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R3     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R4     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R3     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R4     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R3     asm _volatile_(".word 0x00851508\n" :: "x10"); // 0R3     asm _volatile_(".word 0x0085208\n" :: "x10"); // 0R4     asm _volatile_(".word 0x0085208\n" :: "x10"); // 0R3     asm _volatile_(".word 0x0085208\n" :: "x10"); // 0R4     asm _volatile_(".word 0x0085208\n" :: "x10"); // 0R4     asm _volatile_(".word 0x0885208\n" :: "x10"); // 0R4</pre> |          | 00010             | 1240:         fd842783           1244:         60078593           1248:         chacha20qr1           1246:         chacha20qr2           1256:         chacha20qr3           1254:         chacha20qr3           1254:         chacha20qr3           1254:         chacha20qr3           1255:         chacha20qr3           1256:         chacha20qr3           1256:         chacha20qr3           1256:         chacha20qr3           1260:         chacha20qr3           1264:         chacha20qr3 | <pre>mv a0,a5<br/>lw a5,-40(s0)<br/>mv a1,a5<br/>a0,a0,a1<br/>a0,a0,a1<br/>a0,a0,a1<br/>a0,a0,a1<br/>a0,a0,a1<br/>a0,a0,a1<br/>a0,a0,a1<br/>a0,a0,a1<br/>a0,a0,a1<br/>mv a5,a0</pre> |             |   |

| N N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                   | <u>u</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0002                                                                                                                                                                                 |             | 2 |

| Debugger Console 🕄 📕 📕 💭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | Consol 🖾 🏹        | asks 🔝 Proble 🔘 Ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ecut 🤌 Debug 🕞 iProf 🛛                                                                                                                                                               | 🛛 Memor 🛛 🖻 |   |

| tform Launch [Imperas - Connect to running simulator] mpd.exe (7.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                      |             |   |

| <pre>gned int), 1, fp)) {     tbug (cpu0) &gt; 32         res = processLine(res, word);     bug (cpu0) &gt; processLine (input=2222400358, word=2804990272) at te </pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | -                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | m instructio<br>onal state r                                                                                                                                                         |             |   |

CpuManagerMulti started: Thu Rug 23 12:02:30 2018

| Info (OR_OF) Target 'iss/cpu0' has                                                                                                                      | object file rea                                         | d from 'app]                                 | lication/te                         | est_custom.f                        | 21SCV32            | lelf'        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------|-------------------------------------|-------------------------------------|--------------------|--------------|

| Info (OR_PD) LOAD 0x00017<br>Info (OR_OF) Target 'iss/cpu0' has                                                                                         | 000 0x00010000 (<br>270 0x00028270 (                    | 0x00010000 (<br>0x00028270 (                 | 0x00017270<br>0x000009c0            | 0x00017270<br>0x00000a24            | R-E<br>RM-         | 1000<br>1000 |

| Info (OR_PH) Program Headers:<br>Info (OR_PH) Type Offset                                                                                               | VirtAddr i                                              | Physiode I                                   | FileSi+                             | HenSiz                              | Flags              | Olice        |

|                                                                                                                                                         | 000 0::00000000 0<br>010228(processL<br>01022c(processL | 0x00000000 (<br>ine*c): fca4<br>ine*10): fct | 0x0000000c<br>42e23 sw<br>542c23 sw |                                     | R-E<br>(0)<br>(s0) | 1000         |

| Info 1333: 'iss/cpu0', 0x000000000<br>Info 1334: 'iss/cpu0', 0x0000000000<br>Info 1335: 'iss/cpu0', 0x0000000000<br>Info 1336: 'iss/cpu0', 0x0000000000 | 010238(process).<br>01023c(process).                    | ine+1c): fea<br>ine+20): 000                 | c42783 lw<br>078513 wv              | a5,-20<br>a5,-20<br>a0,a5<br>a5,-40 | (08)               |              |

| Info a5 84772366 -> a730c140<br>Info 1337: 'iss/cpu0', 0x0000000000<br>Info 1338: 'iss/cpu0', 0x0000000000                                              |                                                         |                                              |                                     |                                     |                    |              |

| Info a0 84772366 -> e2262347<br>Info 1339: 'iss/cpu0', 0x0000000000<br>Info a0 e2262347 -> 5e207451                                                     | 01024c(processL                                         | ine+30); cha                                 | acha20gr2 a                         | 0,a0,a1                             |                    |              |

| Info 1340: 'iss/cpu0', 0x0000000000<br>Info a0 6e207451 -> 106511c9<br>Info 1341: 'iss/cpu0', 0x0000000000                                              |                                                         |                                              | 1999 B. 199                         |                                     |                    |              |

| Info a0 10b511c9 -) c2e844db<br>Info 1342: 'iss/cpu0', 0x0000000000                                                                                     |                                                         |                                              |                                     |                                     |                    |              |

| Info a0 c2e844db -> 853b65d8<br>Info 1343t 'iss/cpu0', 0x0000000000<br>Info a0 859b65d8 -> ba49822a                                                     | 01025c(processl.                                        | ine+40): cha                                 | acha20gr 2 a                        | 90,a0,a1                            |                    |              |

| Info 1344: 'iss/cpu0', 0x0000000000<br>Info a0 ba49822a -> 79436a1d                                                                                     | 010260(processL                                         | ine+44): cha                                 | acha20gri a                         | 0,a0,a1                             |                    |              |

| Info 1345: 'iss/cpu0', 0x000000000                                                                                                                      | 010264(processL                                         | ine+48): cha                                 | acha20qr4 /                         | 0.a0.a1                             |                    |              |

| Info a0 79436a1d -> 39d5aeef<br>Info 1346: 'iss/cpu0', 0x0000000000<br>Info a5 a730c140 -> 39d5aeef                                                     | 010268(processi.                                        | ine+4c); 000                                 | 050793 mu                           | a5.a0                               |                    |              |

| Info 1347; '155/cpu0', 0x0000000000<br>Info 1348; '155/cpu0', 0x000000000<br>Info 1349; '155/cpu0', 0x000000000<br>RES = 84772366<br>Info               | 010270(processL                                         | ine+54); fea                                 | c42783 lw                           | a5,-20(<br>a5,-20(<br>a0,a5         |                    |              |

| Info                                                                                                                                                    |                                                         |                                              |                                     |                                     |                    |              |

| Info Type : risc<br>Info Nominal MIPS : 100<br>Info Final program counter : 0x10<br>Info Simulated instructions: 677./<br>Info Simulated MIPS : 1209    | New                                                     |                                              |                                     |                                     |                    |              |

| Info<br>Info                                                                                                                                            |                                                         |                                              | 11503                               | 3011                                |                    | y            |

- RISC-V processor DV problem

- Verification flow overview

- RISC-V reference models

- Simple step-and-compare flow

- Complex step-and-compare flow

- Results

- Conclusion

# Simple Step-and-Compare Flow

# mperas

- Goal is to test basic instructions

- riscvOVPsim reference simulator is run separately from RTL simulator

- Results are embedded in the Specman scoreboard

- Tests are then self-checking

- Provides partial testing of multi-hart as tests and expected results can be generated on a per-hart basis

- Similar to flow with Google riscv-dv shown earlier

- Specman test environment with scoreboard used instead of post-simulation trace compare

- Added support for bit manipulation instructions to riscv-dv

# riscvOVPsim Reference Model

Imperas riscvOVPsim Compliance Simulator

- Industrial quality, free ISS / reference model for instruction testing

- <u>https://www.ovpworld.org/info\_riscv</u>

- Model is built using Open Virtual Platforms (OVP) APIs

- Implements full RISC-V envelope

- Configurable for all features and spec versions

#### Adding Support for Bit Manipulation Imperas Instructions to riscv-dv Instruction **Stream Generator** class riscv b instr extends riscv instr; rand riscv reg t rs3; bit has rs3 = 1'b0;'uvm object utils(riscv b instr) function bit [6:0] get opcode(); case (instr name) inside function new(string name = ""); ANDN, ORN, XNOR, GORC, SLO, SRO, ROL, ROR, SBCLR, SBSET, SBINV, SBEXT, super.new(name); GREV: get opcode = 7'b0110011; endfunction SLOI, SROI, RORI, SBCLRI, SBSETI, SBINVI, SBEXTI, GORCI, GREVI, CMIX, CMOV, FSL: get opcode = 7'b0010011; virtual function void set rand mode(); super.set rand mode(); default: get opcode = super.get opcode(); has rs3 = 1'b0; endcase case (format) inside endfunction R FORMAT: begin if (instr\_name inside {CLZW, CTZW, PCNTW, SEXT\_B, SEXT\_H, CLZ, CTZ, PCNT, BMATFLIP, CRC32 B, CRC32 H, CRC32 W, CRC32C B, CRC32C H, CRC32C W, CRC32 D, CRC32C D}) begin has rs2 = 1'b0;end end R4 FORMAT: begin has imm = 1'b0; has rs3 = 1'b1; Add support for instructions end I FORMAT: begin has rs2 = 1'b0; Add support for test generation if (instr name inside {FSRI, FSRIW}) begin has rs3 = 1'b1; end end endcase endfunction

#### Page 22

© 2021 Imperas Software Ltd.

#### DVCon 2021

- RISC-V processor DV problem

- Verification flow overview

- RISC-V reference models

- Simple step-and-compare flow

- Complex step-and-compare flow

- Results

- Conclusion

## Complex Step-and-Compare Flow

# mperas

- Reference model and simulator (Imperas M\*DEV simulator) are run in parallel with RTL simulator (Cadence Xcelium)

- Reference model and RTL Device Under Test (DUT) are stepped in parallel

- This flow enables sync of the RTL DUT and reference model for interrupts and both asynchronous and synchronous events

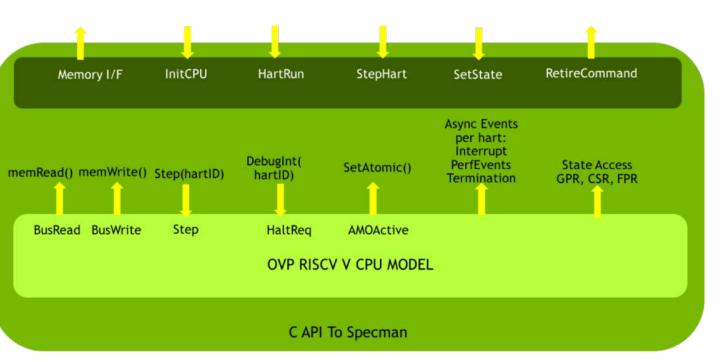

# RISC-V Model with Specman Encapsulation

Effectively the same as the SystemVerilog encapsulation

Imperas

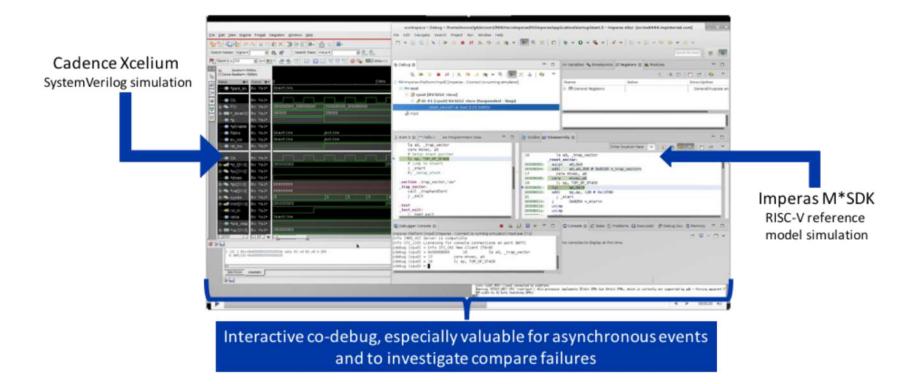

### Interactive Co-Debug is Enabled by the Step-and-Compare Environment

Imperas

- RISC-V processor DV problem

- Verification flow overview

- RISC-V reference models

- Simple step-and-compare flow

- Complex step-and-compare flow

- Results

- Conclusion

# **RISC-V Processor IP**

- RV64IMACBNSU

- 64-bit RISC-V core with extensions including

- Integer

- Multiply

- Atomic

- Compressed

- Bit manipulation

- Machine/supervisor/user modes

- Debug mode

- Custom instructions

- Custom interrupt/event support (e.g. error events)

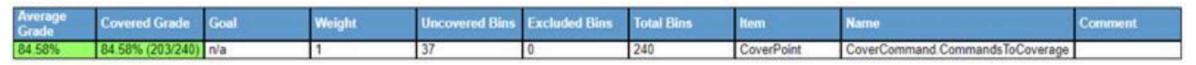

# Instruction Functional Coverage Results from Simple Flow

ISA coverage report for IMACB plus custom commands and non-supported spec (e.g. F as an illegal command)

| Average<br>Grade | Covered<br>Grade | Goal | Weight | Uncovered Bins | Excluded Bins | Total Bins | Item       | Name                                  | Comment |

|------------------|------------------|------|--------|----------------|---------------|------------|------------|---------------------------------------|---------|

| 100.00%          | 100.00% (5/5)    | n/a  | 1      | 0              | 0             | 5          | CoverPoint | CoverJumpBranchCommandsSeq.JBSequence |         |

ISA coverage report for branch jump sequences: loops, backward, forward branches.

|   | Average<br>Grade | Covered<br>Grade | Goal | Weight | Uncovered Bins | Excluded Bins | Total Bins |            | Name                          | Comment |

|---|------------------|------------------|------|--------|----------------|---------------|------------|------------|-------------------------------|---------|

| 1 | 00.00%           | 100.00% (5/5)    | n/a  | 1      | 0              | 0             | 5          | CoverPoint | CoverMultiCycleSeq.MCSequence |         |

ISA coverage report for multicycle sequential insertion.

Imperas

# **Function Coverage Results**

# mperas

| Average<br>Grade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Covered Grade     | Goal | Weight | Uncovered Bins | Excluded Bins | Total Bins | ltem       | Name                                           | Comment |