SAN JOSE, CA, USA FEBRUARY 28 - MARCH 3, 2022

### RISC-V Design Verification solutions

Larry Lapides, Imperas Software

## Agenda

- Introduction to Imperas

- Why RISC-V?

- RISC-V processor design verification (DV) issues

- 5 levels of RISC-V DV methodology

- Key technologies: reference models, verification IP

- Summary

## Agenda

- Introduction to Imperas

- Why RISC-V?

- RISC-V processor design verification (DV) issues

- 5 levels of RISC-V DV methodology

- Key technologies: reference models, verification IP

- Summary

- Imperas founding team has background in Electronic Design Automation (EDA) tools, and FPGA and processor IP companies

- Imperas founding team saw the need for tools and methodology similar to EDA for software debug, test and analysis, based on software simulation

- Just as no SoC is developed without significant simulation, and with verification tools on top of simulation, we believe the embedded community is evolving so that no embedded system will be shipped without significant simulation-based verification of software

- Key Imperas differentiation: Imperas products have been architected from the tool requirements down, not from the modeling requirements up

- With the introduction and adoption of RISC-V, Imperas has added DV technology and methodology to the portfolio

- Q2 2016: Design Automation Conference Imperas first learns about RISC-V looks academic and fragmented

- Q4 2016: RISC-V Workshop (@ Google) 350 attendees from serious companies, and the ISA looks to be converging

- Q1 2017: Imperas joins the RISC-V Foundation; build first RISC-V processor model

- Q3 2017: Imperas starts participating in the Compliance Working Group; builds/donates ISS and tests

- Q1 2018: Imperas introduces methodology for adding/optimizing custom instructions for RISC-V cores

- Q2 2018: First paying customer using Imperas RISC-V models for software development and design verification (DV)

- Q1 2019: First tape out of RISC-V SoC based on using Imperas model as DV reference model

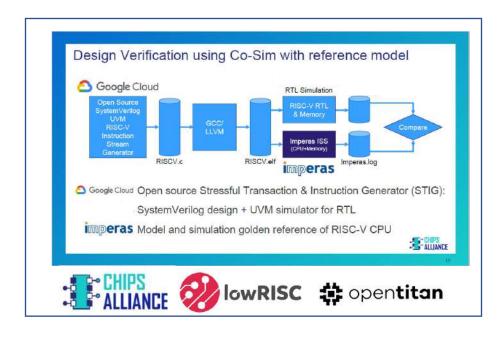

- Q2 2019: Imperas starts collaborating with Google on DV flows with instruction stream generator

- Q1 2020: Imperas starts working with the OpenHW Group and individual members on DV of Core-V cores

- Q1 2021: Imperas presents 2 papers on RISC-V processor DV at the DVCon Silicon Valley conference (with OpenHW, Nvidia Networking)

- Q4 2021: Imperas introduces ImperasDV RISC-V verification product line

## Imperas RISC-V Customers and Partners

### The most complex RISC-V processor projects use Imperas

#### Users

- Nagravision

- Nvidia Networking (Mellanox)

- EM Micro US

- Silicon Labs

- Dolphin Design

- NXP

- lowRISC (lbex)

- RISC-V processor IP vendor

- Top-tier systems company (Al application)

- Top-tier consumer electronics company (AR/VR application)

- NSITEXE (DENSO subsidiary)

- Startup building accelerator based on multiprocessor RV64

- Japanese government projects "TRASIO" and "RVSPF"

- Numerous universities around the world

#### **Partners**

- RISC-V Intl (compliance, bitmanip, crypto, various events)

- OpenHW (verification working group)

- CHIPS Alliance (verification working group)

- Google (for open source ISG, & co-author DV papers)

- Valtrix (test generation tools)

- Andes (processor IP vendor)

- SiFive (processor IP vendor)

- Codasip (processor IP vendor)

- MIPS (processor IP vendor)

## Agenda

- Introduction to Imperas

- Why RISC-V?

- RISC-V processor design verification (DV) issues

- 5 levels of RISC-V DV methodology

- Key technologies: reference models, verification IP

- Summary

- RISC-V is an open standard instruction set architecture (ISA) that began in 2010 at the University of California, Berkeley

- Unlike most other ISAs, RISC-V is provided under open source licenses that do not require fees to use

- This is just the architecture, not the processor implementation

- Unlike other academic designs which are typically optimized only for simplicity of exposition, the designers intended that the RISC-V instruction set be usable for practical computers

- While the ISA is a comprehensive RISC architecture, the RISC-V specification allows for users to add custom features (instructions, CSRs, ...)

- The freedom, and not the free, is why RISC-V usage is growing so fast

# Freedom Enables Domain Specific Processing

- RISC-V is growing in market segments where x86 (PCs, data centers) and Arm (mobile) architectures are not dominant

- Small microcontrollers for SoC management, replacing proprietary cores

- Verticals such as IoT and AI/ML

- Horizontal markets such as security

- The freedom of the open ISA enables users to develop differentiated domain specific processors

- RISC-V users include traditional semiconductor companies, and embedded systems companies now practicing vertical integration by developing their own SoCs

## Agenda

- Introduction to Imperas

- Why RISC-V?

- RISC-V processor design verification (DV) issues

- 5 levels of RISC-V DV methodology

- Key technologies: reference models, verification IP

- Summary

### Challenges in RISC-V Processor DV

- Feature selection and design choices require serious consideration due to implications of every decision

- Experienced processor teams know the costs associated with every feature

- Every addition dramatically compounds verification complexity

- Costs of simple added feature can be huge and unknown to inexperienced teams

- Adds schedule, resources, quality costs == big risks

- As of 2021, no off-the-shelf toolkit/products available for DV of processors

- No EDA vendor has 'RISC-V CPU DV kit' product

- There are in-house proprietary solutions in CPU developers (e.g. Intel, AMD, Arm, ...)

- Building your own processor adds schedule, resources, quality costs ... and risks

- Current SoC cost is 50% for HW DV (with CPUs bought in as proven IP)

- Developing own CPU adds huge DV incremental schedule, resources, quality challenges

## Agenda

- Introduction to Imperas

- Why RISC-V?

- RISC-V processor design verification (DV) issues

- 5 levels of RISC-V DV methodology

- 1) Hello World

- 2) Self-checking tests (e.g. Berkeley torture tests pre-2018)

- 3) Post-simulation trace log file compare

- 4) Synchronous step-and-compare

- 5) Asynchronous step-and-compare

- Key technologies: reference models, verification IP

- Summary

## 3) Post-Simulation Trace Log File Compare (Entry Level DV)

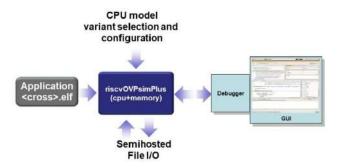

Imperas riscvOVPsimPlus Reference Simulator

- Process

- use random generator (ISG) to create tests

- during simulation of ISS write trace log file

- during simulation of RTL write trace log file

- at the end of both runs, run logs through compare program to see differences / failures

- ISS: riscvOVPsimPlus includes Trace and GDB interface

- Free ISS: https://www.ovpworld.org/riscvOVPsimPlus

- ISG: riscv-dv from Google Cloud / Chips Alliance

- Free ISG: https://github.com/google/riscv-dv

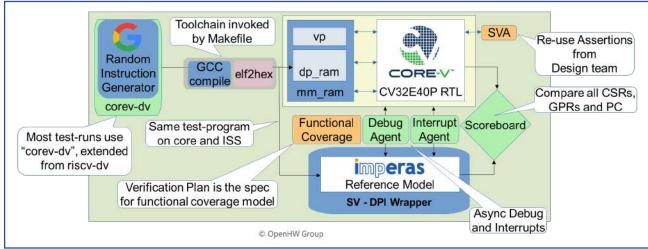

## 5) Asynchronous Step-Compare (Highest Quality DV Methodology)

mperas

- Design features needing this methodology include OoO and multi-issue pipeline, multi-hart processor, debug mode, interrupts, ...

- Example SystemVerilog components

- tracer: Reports instructions for checking and register writebacks

- step\_and\_compare: Manages the reference model and checks functionality

- interrupt\_assert: Properties for interrupt coverage/checking

- debug\_assert: Properties for debug coverage/checking

- Typically hard, complex, and expensive to get working

- Challenge is extracting async info from microarchitecture RTL pipeline

2<sup>nd</sup> generation CV32E40P OpenHW flow (2H2020) (Imperas model encapsulated in SystemVerilog)

### Asynchronous Step-Compare Summary

- Instruction by instruction lockstep comparison (includes async events)

- Comparison of execution flow, of program data, of programmers and internal state

- Immediate comparison

- Allows for debug introspection at point of failure very powerful

- Does not waste execution cycles after failure

- Includes focus on async events, control flow, and hardware real time effects

- Supports multi-hart processors and out-of-order / multi-issue pipelines

- Can be hard to develop & set up (depends on RTL DUT tracer features and pipeline understanding)

- Can be expensive in terms of time, resources, licenses => costs a lot per bug found

- But the bugs are even more expensive if not found early enough ...

- Async step-compare is the most comprehensive and most efficient DV approach

- Next steps for async step-compare: standards for the test bench; verification IP

## Agenda

- Introduction to Imperas

- Why RISC-V?

- RISC-V processor design verification (DV) issues

- 5 levels of RISC-V DV methodology

- Key technologies: reference models, verification IP

- Summary

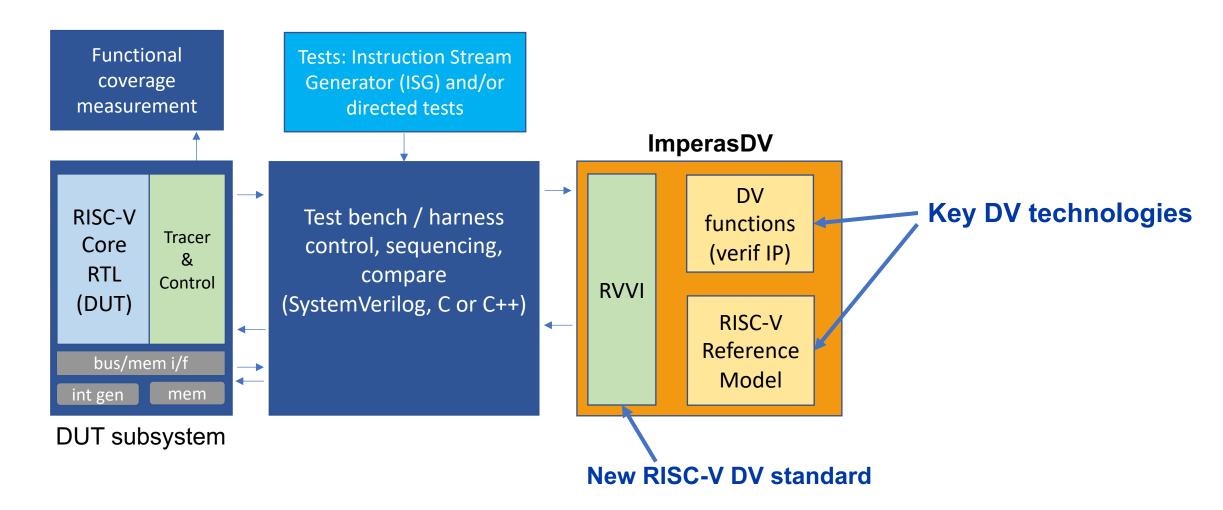

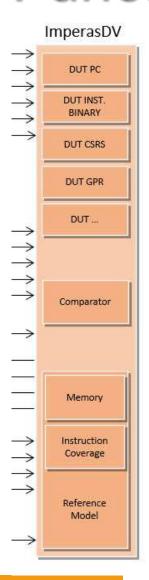

## RISC-V Processor DV Environment has 5 Major Components

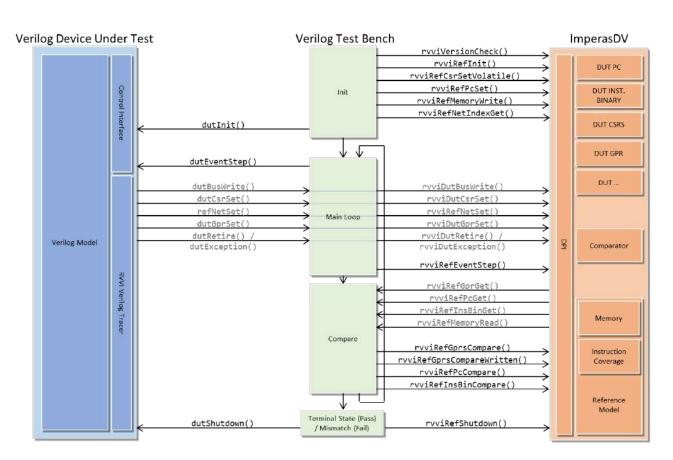

## RVVI: RISC-V Verification Interface Standard for Connecting to Test Harness

DUT subsystem

- https://github.com/riscv-verification/RVVI (Public Open Standard)

- RVVI-VLG

- Verilog DUT interfaces

- RVVI-VLG state streaming 'tracer' data

- RVVI-VLG nets implementation dependent (Interrupts, Debug)

- Handles multi-hart, multi-issue, Out-of-Order

#### **ImperasDV**

- RVVI-API

- Controls DV subsystem and reference model

- RVVI\_state RISC-V Verification Interface State

- RVVI\_control RISC-V Verification Interface Control

- RVVI\_io RISC-V Verification Interface IO (Interrupts, Debug)

- RVVI\_bus RISC-V Verification Interface (Data, Instruction Bus)

- Supports SystemVerilog, C, C++ testbenches

DUT subsystem

- The key component the DUT being tested

- Includes memory model and bus interfaces

- Includes interrupt generator

- Requires a tracer to provide appropriate data to the test bench

- Requires control interface so test bench can step through events

- Quality of the tracer determines the potential capabilities of the DV environment

## RISC-V Model Requirements Not Just for DV; Also for SW Dev

- Model the ISA, including all versions of the ratified spec, and stable unratified extensions

- Easily update and configure the model for the next project

- User-extendable for custom instructions, registers, ...

- Model actual processor IP, e.g. Andes, SiFive, OpenHW, Codasip, MIPS, ...

- Well-defined test process including coverage metrics

- Interface to other simulators, e.g. SystemVerilog, SystemC, Imperas virtual platform simulators

- Interface to software debug tools, e.g. GDB/Eclipse, Imperas MPD

- Interface to software analysis tools including access to processor internal state, etc.

- Interface to architecture exploration tools including extensibility to timing estimation

- Most RISC-V ISSs can meet one or two of these requirements

- Imperas models and simulators were built to satisfy these requirements, and matured through usage on non-RISC-V ISAs over the last 12+ years

# OVP Library of RISC-V Fast Processor Models

- Existing Imperas Open Virtual Platforms (OVP) Fast Processor Models of ...

- Generic or envelope models of RV32/64 IMAFDCEVBHKP M/S/U privilege modes

- Models of processor IP vendors: Andes, Codasip, MIPS, OpenHW, SiFive

- Custom models for users building their own RISC-V processors

- Custom instructions easily added by user or by Imperas

- New instructions are added in side file so as not to perturb the verified model

- Imperas tools work with the complete processor model, including the custom instructions

- Custom instructions can be analyzed for effectiveness using instruction coverage, profiling tools

- Video demo: http://www.imperas.com/risc-v-custom-instruction-design-and-verification-flow

- Models are built using Test Driven Development (TDD) methodology

- Tests are built at the same time as features are added

- Continuous Integration (CI) test flow used

- > 15,000 directed tests for models + simulator

- Additional testing by processor IP vendors to validate models

"The Imperas virtual platform solutions for software development, debug and test, along with their open-source models, will help accelerate SoC and embedded software development for our customers." Charlie Hong-Men Su, Ph.D., Andes Technology CTO

"The donation of a robust, commercial-quality simulator – riscvOVPsim – will enable our customers to adopt RISC-V even faster. This is the level of close industry collaboration that will drive the successful adoption of RISC-V."

Yunsup Lee, co-founder and CTO, SiFive

### Imperas is the Reference Model

http://www.imperas.com/riscv

- Imperas provides full RISC-V Specification envelope model

- Industrial quality model /simulator of RISC-V processors for use in compliance, verification and test development

- Complete, fully functional, configurable model / simulator

- All 32bit and 64bit features of ratified User and Privilege RISC-V specs

- Vector extension, versions 0.7.1, 0.8, 0.9, 1.0

- Bit Manipulation extension, versions 0.91, 0.92, 0.93, 1.0.0

- Hypervisor version 0.6.1

- K-Crypto Scalar version 0.7.1, 1.0.0

- Debug versions 0.13.2, 0.14, 1.0.0

- Model source included under Apache 2.0 open source license

- Used as reference by :

- Mellanox/Nvidia Networking, Seagate, NSITEXE/Denso, Google Cloud, Chips Alliance, lowRISC, OpenHW Group, Andes, Valtrix, SiFive, Codasip, MIPS, Nagravision, Silicon Labs, RISC-V Compliance Working Group, ...

### Imperas is used as RISC-V Golden Reference Model

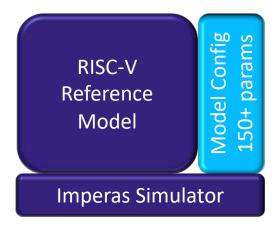

### Imperas Model Extensibility

RISC-V

Reference

Model

Model

User Extension:

custom

instructions

& CSRs

Imperas Simulator

- Separate source files and no duplication to ensure easy maintenance

- Imperas or user can develop the extension

- User extension source can be proprietary

Imperas develops and maintains base model

- Base model implements RISC-V specification in full

- Fully user configurable to select which ISA extensions

- Fully user configurable to select which version of each ISA extension

- Updated very regularly as ISA extension specification versions change

- Fully user configurable for all RISC-V specification options

- e.g. implemented optional CSRs, read only or read/write bits etc...

Imperas provides methodology to easily extend base model

- Templates to add new instructions

- Code fragment for adding functionality

- 100+ page user guide/reference manual with many examples

- Includes example extended processor model

## Imperas model is architected for easy extension & maintenance

Characterize C Application

- Simulation

- Trace / Debug

- Function Profiling

- Cross compiled C application targeting RV32IM

- Character stream encoder, with ChaCha20 encryption algorithm

- IA simulation

- Imperas RISC-V ISS with configurable model of RISC-V specification selecting RV32IM

- Semihosting

- Enables bare metal application to very simply access host I/O

- >runs fast

- Over 1 billion instructions a second (standard PC)

- Linux and Windows supported host OS

```

test_c.c 23

unsigned int processLine(unsigned int res, unsigned int word) {

res = qrl c(res, word);

res = gr3 c(res, word);

res = qr4_c(res, word);

int main(void) {

const char *customData = "application/custom.data";

FILE *fp = fopen(customData, "r");

unsigned int res = 0x84772366;

unsigned int word;

unsigned int cnt=0:

unsigned int iter=0;

while (iter++ < 16) {

while (fread(&word, sizeof(unsigned int), 1, fp)) {

res = processLine(res, word):

CpuManagerMulti (32-Bit) v9999999 Open Virtual Platform simulator from www.IMPERAS.com.

Copyright (c) 2005-2018 Imperas Software Ltd. Contains Imperas Proprietary Information.

icensed Software, All Rights Reserved.

fclose(fp)

CpuManagerMulti started: Thu Aug 23 11:19:21 2018

printf("RES = NO8

0x90000000 0x90010000 0x00010000 0x000173c8 0x000173c8 R-E

0x000173c8 0x000283c8 0x000283c8 0x000009c0 0x00000a24 RM-

(OR_OF) Target 'iss/cpu0' has object file read from 'application/exception.RISCV32.elf'

Offset VirtAddr PhysAddr FileSiz MemSiz Flag

0x00001000 0x00000000 0x00000000 0x0000000c 0x0000000c R-f

Info CPU 'iss/cpu0' STATISTICS

Final program counter : 0x100ac

Simulated tipe

Elapsed time

: 1.14 seconds

: 11.31x faster

Real time ratio

EpullanagerHulti finished: Thu Aug 23 11:19:22 2018

```

© 2022 Imperas Software Ltd.

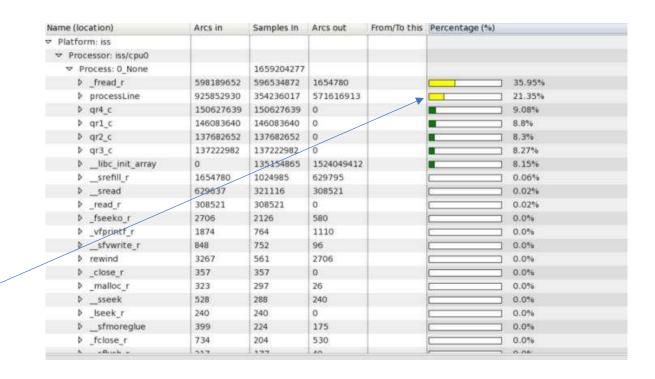

- Same C application

- IA+E simulation

- Sampled profiling with call stack analysis

- ➤ Shows proportion of time spent in each application function

- >21.35% spent in processLine

**Imperas**

Characterize C Application

- Simulation

- Trace / Debug

- Function Profiling

Add to Model

### Add Custom Instructions to Application

**Imperas**

- Inline assembly using new instructions replacing C code

- 4 new instructions

- Cross compile using standard tool

- Run on IA simulator

- When simulate: unimplemented instruction exception

- As the instructions have not yet been added to the simulator model

```

// Custom instruction test for Chacha20

#include <std10.h>

unsigned int processline(unsigned int input, unsigned int word){

unsigned int res = input;

asm __volatile__("mv x10, %0" :: "r"(res));

asm __volatile__("mv x11, %0" :: "r"(word));

asm __volatile__(".word 0x00050508\n" ::: "x10");

asm __volatile__(".word 0x00851508\n" ::: "x10");

asm __volatile__(".word 0x00B52508\n" ::: "x10");

asm __volatile_ (".word 0x00853508\n" ::: "x10");

asm __volatile__(".word 0x00B50508\n" ::: "x10");

// QR1

asm __volatile__(".word 0x00851508\n" ::: "x10");

asm __volatile__(".word 0x00B52508\n" ::: "x10");

// OR3

asm __volatile__(".word 0x00B5350B\n" ::: "x10");

asm __volatile__("mv %0,x10" : "=r"(res));

return res:

CpuManagerMulti (32-Bit) v99999999 Open Virtual Platform simulator from www.IMPERAS.com.

int mai Copyright (c) 2006-2018 Imperas Software Ltd. Contains Imperas Proprietary Information.

icensed Software, All Rights Reserved.

Visit www.IMPERSS.com for multicore debug, verification and analysis solutions,

CouManagerMulti started: Thu Aug 23 11:34:51 2018

0x00000000 0x00010000 0x00010000 0x00017270 0x00017270 R-E 1000

0x00017270 0x00028270 0x00028270 0x000009e0 0x00000a24 RM-

Info (OR.OF) Target 'iss/cpu0' has object file read from 'application/exception,RISCV32.elf'

iss/cpu0' 0x00010248 00b5050b custom1; Illegal instruction - extension X (non-standard extensions present) absent or inactive

: riscv (RV321M)

: 100

: run too short for meaningful result

Info SIMULATION TIME STATISTICS

Simulated time

: 0.00 seconds

CpuManagerMulti finished; Thu Aug 23 11:34:51 2018

```

# Add Custom Instructions to Model and Re-Simulate

mperas

- Use standard Open Virtual Platforms (OVP) instruction modeling APIs to add new instructions (and optional state) as new extension library

- Easy to extend decode table, add efficient behavioral JIT code

- Optionally can call directly into user's provided C function of behavior

- Compile and link model extension library

- Simulate IA with ISS plus standard model extended with new library

- Instruction count and simulated time have been reduced

```

// Create the RISCV decode table

static vmidDecodeTableP createDecodeTable(void)

vmidDecodeTableP table = vmidNewDecodeTable(RISCV_INSTR_BITS, RISCV_EIT_LAST);

// Emit code implementing exchange instruction

// R-Type instruction in custom-0 encoding space:

// opcode [6:0] = 00 010 11

static void emitChaCha20(

// funct3[14:12] = 0,1,2,3 (QR1-4)

vmiProcessorP processor.

// funct7[31:25] = 0000000

vmiosObjectP object,

instruction,

// rs2[24:20]

rotl

// rd[11:7]

// extract instruction fields

Uns32 rd = RD(instruction);

DECODE ENTRY(0, CHACHA200R2, "[00000000......001.....0001011]");

Uns32 rs1 = RS1(instruction);

DECODE_ENTRY(0, CHACHA29QR3, "|0000000......010.....0001011|");

Uns32 rs2 = RS2(instruction);

DECODE ENTRY(8, CHACHA20QR4, "[00000000......011.....0001011]");

vmiReg reg_rs1 = vmimtGetExtReg(processor, &object->rs1);

return table;

vmiReg reg_rs2 = vmimtGetExtReg(processor, &object->rs2);

vmiReg reg_tmp = vmimtGetExtTemp(processor, &object->tmp);

vmimtGetR(processor, RISCV_REG_BITS, reg_rs1, object->riscvRegs[rs1]);

vmimtGetR(processor, RISCV REG BITS, reg rs2, object->riscvRegs[rs2]);

opyright (c) 2005-2018 Imperas Software Ltd. Contains Imperas Proprietary Information.

vmimtBinopRRR(32, vmi_XOR, reg_tmp, reg_rs1, reg_rs2, 0);

icensed Software, All Rights Reserved,

isit www.IMPERRS.com for multicore debug, verification and analysis

vmimtBinopRC(32, vmi ROL, reg tmp, rotl, 0);

puManagerMulti started: Thu Aug 23 11:41:32 201

vmimtSetR(processor, RISCV REG BITS, object->riscvRegs[rd], reg tmp);

$IMPERAS_VLNV/riscv.ovpworld.org/semihosting/riscv32Newlib/1.0/model

instructionExtensionLib

Final program counter : 0x100ac

Simulated instructions: 677,012,570

```

nfo SIMULATION TIME STATISTICS

nfo Simulated time :

Elapsed time

: 0,50 seconds : 0,02 seconds : 0,53 seconds : 12,81x faster

puManagerMulti finished: Thu Aug 23 11:41:33 2018

- Simulator has many trace features built in

- See new custom instructions in trace disassembly

- Can select when/where to turn trace on/off

- Very efficient tracing

```

CpuManagerMulti started: Thu Aug 23 12:02:30 2018

Info (OR_OF) Target 'iss/cpu0' has object file read from 'application/test_oustom_RISCV32.elf'

Info (OR_PH) Program Headers;

VirtAddr PhysAddr FileSiz MemSiz Flags Align

Info (OR_PD) LOAD

0x00000000 0x00010000 0x00010000 0x00017270 0x00017270 R-E 1000

0x00017270 0x00028270 0x00028270 0x000009c0 0x00000a24 RM-

Info (OR_OF) Target 'iss/cpu0' has object file read from 'application/exception,RISCV32,elf'

Info (OR_PH) Program Headers;

VirtAddr PhysAddr FileSiz MemSiz

0x00001000 0x00000000 0x00000000 0x0000000c 0x0000000c R-E 1000

Info 1330: 'iss/cpu0', 0x0000000000010228(processLine*c): fca42e23 sw

a0,-36(s0)

Info 1331; 'iss/cpu0', 0x000000000001022c(processLine+10); fcb42c23 sw

al.-40(s0)

Info 1332: 'iss/csu0', 0x000000000010230(processLine+14); fdc42783 lw

a5,-36(s0)

Info a6 a730c140 -> 84772366

Info 1333: 'iss/cpu0', 0x0000000000010234(processLine+18): FeF42623 sw

Info-1334: 'iss/cpu0', 0x000000000010238(processLine+1c); fec42783 lw

a5,-20(a0)

Info 1335; 'sas/cpu0', 0x000000000001023c(processLine+20); 00078513 mv

Info 1336; 'iss/cpu6', 0x0000000000010240(processLine+24); fd842783 lw

a5,-40(s0)

Info a5 84772366 -> a730c140

Info 1337: 'iss/cpu0', 0x0000000000010244(processLine+28): 00078593 mv

Info 1338; 'iss/cpu0', 0x000000000010248(processLine+2c); chacha20gr1 a0,a0,a1

Info a0 84772366 -> e2262347

Info 1339; "iss/cpu0", 0x000000000001024c(processLine+30); chacha20gr2 a0,a0,a1

Info a0 e2262347 -> 5e207451

Info 1340; 'iss/cpu0', 0x0000000000010250(processLine+34); chacha20gr3 a0.a0.a1

Info a0 6e207451 -> 10b511c9

Info 1341; 'iss/cpu0', 0x0000000000010254(processLine+38); chacha20gr4 a0,a0,a1

Info a0 10b511c9 -> c2e844db

Info 1342; 'iss/cpu0', 0x000000000010258(processLine+3c); chacha20grl a0.a0.a1

Info a0 c2e844db -> 859b65d8

Info 1343; 'iss/cpu0', 0x000000000001025c(processLine+40); chacha20gr2 a0,a0,a1

Info a0 859b65d8 -> ba49822a

Info 1344; 'iss/cpu0', 0x0000000000010260(processLine+44); chacha20gr3 a0,a0,a1

Info a0 ba49822a -> 79436a1d

Info 1345; 'iss/cpu0', 0x0000000000010264(processLine*48); chacha20gr4 a0.a0.a1

nfo a0 79436a1d -> 39d5aeef

Info 1346: 'iss/cpu0', 0x0000000000010268(processLine+4c): 00050793 mv

Info a5 a730c140 -> 39d5aeef

Info 1347; "iss/cpu0", 0x0000000000001026c(processLine+50); fef42623 sw

Info 1348; 'iss/cpu0', 0x0000000000010270(processLine+54); Fec42783 lw

a5,-20(s0)

Info 1349; 'iss/cpu0', 0x0000000000010274(processLine+58); 00078513 mu

RES = 84772366

Info CPU 'iss/opu0' STATISTICS

: riscv (RV32IM)

Nominal HIPS

: 100

Final program counter : 0x100ac

Simulated instructions: 677,012,570

```

## mperas

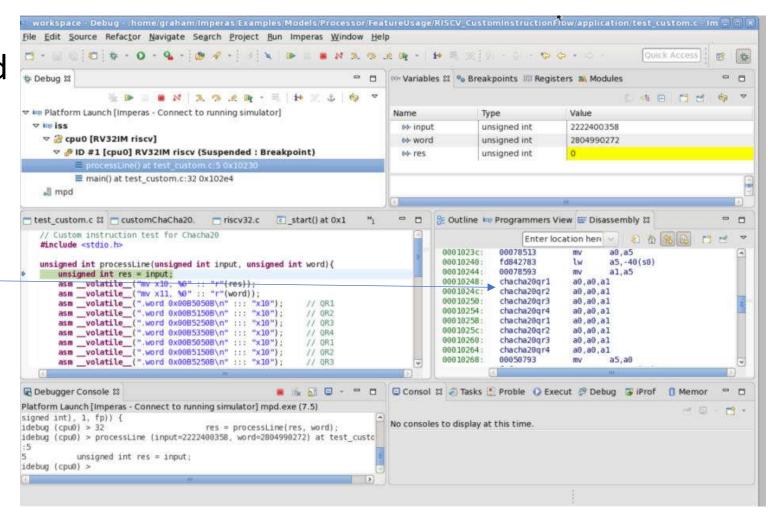

### **Debug Custom Instructions**

- Imperas MPD is Eclipse based source code debug tool

- Can debug using source line or instruction level

- See new custom instructions and any new additional state registers

# Function Profile Application Using Custom Instructions

- IA simulation + timing annotation + custom instructions with sampled profiling

- >Shows where slowest function is

- Now much faster...

- Shows benefits of using custom instructions

- processLine was 21.35% now 14.71%

| Name (location)           | Arcs in   | Samples in | Arcs out  | From/To this | Percentage (%) |

|---------------------------|-----------|------------|-----------|--------------|----------------|

| ♥ Platform: iss           |           |            |           |              |                |

| ♥ Processor: iss/cpu0     |           |            |           |              |                |

| ♥ Process: 0_None         |           | 921006649  |           |              |                |

| ▶ _fread_r                | 635365939 | 633628269  | 1737670   |              | 68.8%          |

| Dlibc_init_array          | 0         | 150138664  | 770867985 |              | 16.3%          |

| ▶ processLine             | 135494635 | 135494635  | 0         | <b>▼</b>     | 14.71%         |

|                           | 1737670   | 1066083    | 671587    |              | 0.12%          |

| ▶ _read_r                 | 340125    | 340125     | 0         |              | 0.04%          |

| ▶ _sread                  | 671429    | 331304     | 340125    |              | 0.04%          |

| b _fseeko_r               | 3849      | 3269       | 580       |              | 0.0%           |

| <pre>Dsfvwrite_r</pre>    | 784       | 688        | 96        |              | 0.0%           |

| Þ _sflush_r               | 599       | 559        | 40        |              | 0.0%           |

| <pre>b _vfprintf_r</pre>  | 1492      | 446        | 1046      |              | 0.0%           |

| Þ rewind                  | 4153      | 304        | 3849      |              | 0.0%           |

| ▶ _malloc_r               | 323       | 297        | 26        |              | 0.0%           |

| ♪ _sseek                  | 528       | 288        | 240       |              | 0.0%           |

| ▶ _lseek_r                | 240       | 240        | 0         |              | 0.0%           |

| b _sfmoreglue             | 399       | 224        | 175       |              | 0.0%           |

| Þ_fclose_r                | 811       | 204        | 607       |              | 0.0%           |

| b _sinit.part.1           | 146       | 146        | 0         |              | 0.0%           |

| <pre>p _fwalk_reent</pre> | 790       | 106        | 684       |              | 0.0%           |

| ▶ _sfp                    | 641       | 96         | 545       |              | 0.0%           |

| ▶ smakebuf r              | 316       | 78         | 238       |              | 0.0%           |

Characterize C Application

- Simulation

- Trace / Debug

- Function Profiling

Develop New Custom Instructions

- Design Instructions

- Add to Application

- Add to Model

Characterize New Instructions in Application

- Simulation

- Trace / Debug

- Function Profiling

mperas

Characterize C Application

- Simulation

- Trace / Debug

- Function Profiling

Develop New Custom Instructions

- Design Instructions

- Add to Application

- Add to Model

Characterize New Instructions in Application

- Simulation

- Trace / Debug

- Function Profiling

Optimize & Document model

- Instruction Coverage

- Line Coverage

- Generate model doc pdf

#### Characterize C Application

- Simulation

- Trace / Debug

- Function Profiling

### Develop New Custom Instructions

- Design Instructions

- Add to Application

- Add to Model

### Characterize New Instructions in Application

- Simulation

- Trace / Debug

- Function Profiling

#### Release & Deploy

- Check RISC-V Compliance

- Use as reference for RTL Design Verification

- Use in Imperas/OVP Platforms, EPKs

- Heterogeneous / Homogeneous

- Multi-core, Many-core

- Imperas Multi-Processor Debug, VAP tools

- Port OS, RTOS (Linux, FreeRTOS...)

- Use in many simulation envs (inc. SystemC)

- Deliver to end users

#### Optimize & Document model

- Instruction Coverage

- Line Coverage

- Generate model doc pdf

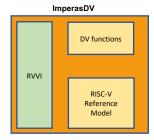

# ImperasDV: RISC-V Verification IP

mperas

- Verification IP is needed for ...

- Ease of use

- Scalability

- Extendability

- Performance

- Debug

- Schedule reduction

### **DV Functions**

- Select model, use variant, configure

- Reference model encapsulation

- Enable instruction coverage

- Includes DUT reference state storage

- Includes synchronization technology

- Can run sync, async, interrupts, debug, multi-hart

- Includes comparison technology

- Comparisons are done on instruction retirement; enables DV of multi-issue and OoO pipeline processors

- Can be used in C/C++ or SystemVerilog test bench / harness

- Uses RVVI-API

- Very simple to use the 'smarts' are built-in

### ImperasDV Setup

- Reference model setup

- Configuration of register and memory initialization

- Selection of what to compare (depends on DUT tracer capabilities)

- PC, GPR, CSR, FPR, VR, decode, net, hart ...

- Select capabilities:

- sync-step-compare or async-step-compare

- Trace and logging set up

- Selection of built-in instruction coverage

- Choice of DV control options

- RISC-V processor developers need to do comprehensive verification of the RTL implementation

- Processor DV methodology has been evolved by Imperas, together with customers and partners

- Asynchronous step-compare methodology provides the most comprehensive, most efficient RISC-V DV flow

- Key technologies include the Imperas OVP reference model and the ImperasDV verification IP

## Thank you!

LarryL@imperas.com