#### UNITED STATES

SAN JOSE, CA, USA FEBRUARY 28 - MARCH 3, 2022

Introduction to RISC-V CPU design verification

Kevin McDermott, Imperas Software

- Welcome and agenda

- Introduction to RISC-V DV

- Imperas News Highlights for DVCon 2022

- Conclusions

## Imperas at DVCon 2022

- Tutorial: 'Introduction to the 5 levels of RISC-V Processor Verification'

- Simon Davidmann and Lee Moore Imperas Software

- Monday February 28th 9:00-11:00am PST

- Presentation: 'Introduction to RISC-V CPU design verification'

- Kevin McDermott Imperas Software

- Tuesday March 1st 12:30-1:00 pm PST

- Presentation: 'Imperas RISC-V Design Verification solutions'

- Larry Lapides Imperas Software

- Tuesday March 1st 1:00-1:30pm PST

# Introduction to RISC-V CPU design verification

## Highlights for this talk

- RISC-V is changing the options that SoC designers have in their tool kits

- RISC-V means many teams are designing new processors, or modifying source of processors

- For RISC-V anybody can be 'an architecture licensee'

- And every CPU needs verifying... in detail... (its not like buying in pre-verified IP)

- Many people are new to CPU DV for the first time

- Traditionally done behind closed doors in commercial/proprietary companies

- This presentation aims to introduce the main approaches of RISC-V CPU DV

- And discusses pros and cons of the different approaches

- Also it introduces the main components needed in any RISC-V processor DV environment

#### Introduction to Imperas Involvement with RISC-V

- Imperas develops simulators, tools, debuggers, modeling technology, and models to help embedded systems developers get their software running...

- ...and hardware developers get their designs correct

- 14+ years, self funded, profitable, UK based, team with much EDA (simulators, verification), processors, and embedded experience

- Staff worked in Arm, MIPS, Imagination, Tensilica, Cadence, Synopsys, ....

- and in verification in EDA on development of Verilog, VCS, SystemVerilog, Verisity and their methodologies

- Started work with customers on RISC-V in 2017

- Contributed to RISC-V compliance since 2018, RISC-V DV since 2019

- Our RISC-V focus is CPU verification

Page 6

- We provide configurable reference models, the fastest highest quality simulators, advanced development tools and the absolute best solution for RISC-V hardware design verification

- 20+ of the leading RISC-V CPU developers use and rely on Imperas solutions

www.imperas.com www.OVPworld.org

© Imperas Software Ltd.

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

- RISC-V (pronounced "risk-five") is an open standard instruction set architecture (ISA) that began in 2010 and is based on established reduced instruction set computer (RISC) principles

- Unlike most other ISA designs, RISC-V is provided under open source licenses that do not require fees to use

- The project began in 2010 at the University of California, Berkeley, but now many current contributors are volunteers not affiliated with the university

- Unlike other academic designs which are typically optimized only for simplicity of exposition, the designers intended that the RISC-V instruction set be usable for practical computers

## Industry innovation on RISC-V

| Hardware |

|----------|

| – RV32 – |

Complexity

Hardware ISA Definition Test Chips

Software

Tests

2010 - 2016

Proof of Concept SoCs Minion processors for power management, communications, ...

**Software** Bare metal software 2017 – 2018

2019 - 2020

Hardware

RV32, privilege

modes, interrupts -

IoT SoCs

**Microcontrollers**

Software

RTOS

**Firmware**

Hardware

– RV64, multi-heart CPUs, vectors, bit manipulation,

hypervisors, debug mode –

> Al SoCs Application processors

Software Linux Drivers Al Compilers

2021

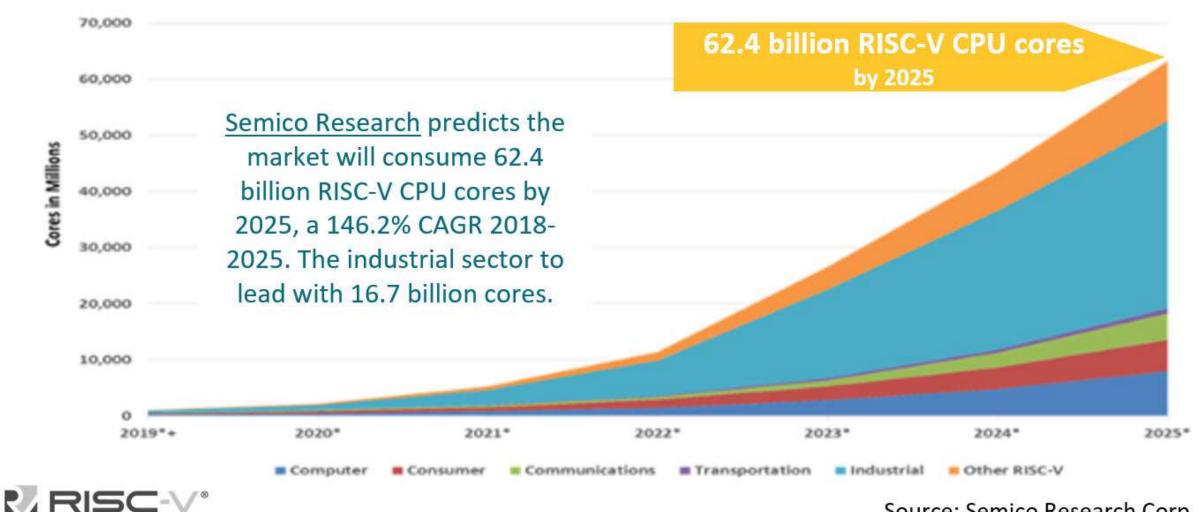

#### Rapid RISC-V growth led by industrial

Source: Semico Research Corp

#### Cloud and data center top

providers like Amazon and Alibaba are designing their own chips.

#### Automotive

is transforming from autonomous vehicles to infotainment to safety, the whole vehicle relies on innovative electronics.

#### **Industrial IoT**

incorporating artificial intelligence in manufacturing and industrial processes. . . .

((( q )))

#### Mobile and

#### wireless continue rapid

evolution with each generation of hardware and increased capability.

#### Consumer and IoT devices bring

incredible innovation and volume with billions of connected devices in the next 5-10 years.

#### Memory was largest

semiconductor category by sales with \$158 billion in 2018, and the fastest-growing.

**RISC-V** adoption spans industries and workloads

#### More than 2,200 RISC-V Members across 70 Countries

|    | 102 Chip                                 | 4 Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | SoC, IP, FPGA                            | ODM, OEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | <b>4 I/O</b><br>Memory, network, storage | <b>13 Industry</b><br>Cloud, mobile, HPC, ML, automotive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | 17 Services                              | 95 Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    | Fab, design services                     | Universities, Labs, other alliances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 42 Software                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | Dev tools, firmware, OS                  | 1,900+ Individuals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Q3 | Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4               | RISC-V engineers and advocates        Q1      Q2      Q3      Q4      Q1      Q2 |

RISC-V membership grew 133% in 2020. In 2021, RISC-V membership has already doubled.

#### RISC-V Innovation Roadmap Al Socs, Application

| Test Chips<br>Software tests<br>Linux portProof of Concept SoCs<br>Minion processors for<br>power management,<br>communications<br>Bare metal software |                                                                                                 | IoT SoCs<br>Microcontrollers<br>RTOS, Firmware<br>Development tools<br>Technical Steering<br>Committee,<br>HPC SIG,<br>GlobalPlatform<br>partnership |                 | processors, Linux<br>Drivers, AI Compilers<br>Dev Board program<br>Development Partners<br>RISC-V Labs, Security<br>response process, AI<br>SIG, Graphics SIG,<br>Android SIG,<br>Communications SIG |                                                                                                         | Industry Adoption<br>Proliferation of RISC-V CPUs across<br>performance and application spectrum<br>RISC-V dominant in universities<br>Strategic and growing adoption in HPC,<br>automotive, transportation, cloud,<br>industrial, communications, IoT,<br>enterprise, consumer, and other<br>applications |                                       |                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|

| 2010 - 2016                                                                                                                                            | 20                                                                                              | 17                                                                                                                                                   |                 | 2018                                                                                                                                                                                                 |                                                                                                         | 2019                                                                                                                                                                                                                                                                                                       | 2020                                  | 2021            |

| ISA Definition<br>RISC-V<br>Foundation                                                                                                                 | Base in<br>Integer<br>point, r<br>divide,<br>compace<br>Priv mo<br>Interru<br>excepti<br>model, |                                                                                                                                                      |                 | s, memory<br>otection,                                                                                                                                                                               | y 2<br>race 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | RISC-V Profiles &<br>Platforms<br>Crypto Scalar<br>Virtual Memory<br>Hypervisor & Advanced<br>interrupt architecture<br>Cache mgt ops<br>Code size reduction*                                                                                                                                              | Cache management phase 2*<br>and more |                 |

| RIS                                                                                                                                                    | <b>-</b> -v* ,                                                                                  | On track, su                                                                                                                                         | bject to change |                                                                                                                                                                                                      | 1                                                                                                       | Trusted Execution<br>Environment*<br>P (Packed SIMD)*                                                                                                                                                                                                                                                      | Technic                               | al Deliverables |

#### RISC-V == Freedom...

#### Freedoms enabled by RISC-V are a huge opportunity

#### RISC-V == Freedom...

#### Freedoms enabled by RISC-V are a huge opportunity

# Freedoms enabled by RISC-V are a huge challenge for verification

the largest change in the industry since? ...

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

## Challenges in RISC-V CPU DV

- Feature selection and choices require serious consideration due to implications of every choice

- Experienced architecture teams know the costs associated with every feature

- Every addition dramatically increases (doubles ?) verification & compounds verification complexity

- Costs of simple added feature can be huge and unknown to inexperienced teams

- Adds schedule, resources, quality costs == big risks...

- As of 2021, No off-the-shelf toolkit/products available for DV of processors

- No EDA vendor has 'RISC-V CPU DV kit' product

- There are in-house proprietary solutions in CPU developers... Intel, AMD, Arm, ...

- Building your own adds schedule, resources, quality costs and risks

- Current SoC cost is 50% for HW DV (with CPUs bought in as proven IP)

- Developing own CPU adds huge DV incremental schedule, resources, quality challenges

# mperas

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

# mperas

## Agenda

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

Note that not all projects have the same requirements, schedule or verification needs – so each project's DV needs may / will differ

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

- "if I can get a program to run then my DV is done... right?"

- "my DV challenge is sorted if I can get Linux to boot on my design..."

- Basically this level of DV is where developer feels if they can get their current compilation of their current program to run (through one path) - then their silicon design job is done

- This may be fine for test chips, research, academic, hobbyists, but NOT for products

- This approach is often due to lack of knowledge or interest in quality, ...

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

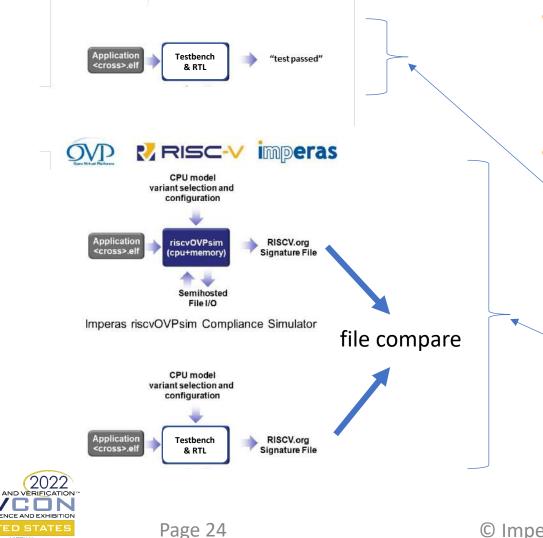

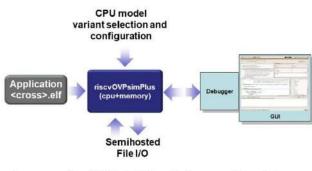

#### **#1: Simple (results) check (1b)** (use e.g. riscvOVPsim ISS from GitHub)

FEBRUARY 28 - MARCH 3, 2023

- Run RTL DUT in testbench

- (no real testbench)

- Just loads & runs the test program

Either

- Each test program checks its results = go/no go test

- Prints message to log

- or writes bit to memory

- Or, then run ISS, write log or signature file

- Compare/diff file results (afterwards)

- This is the approach taken by RISCV International for their architectural validation ("compliance tests")

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

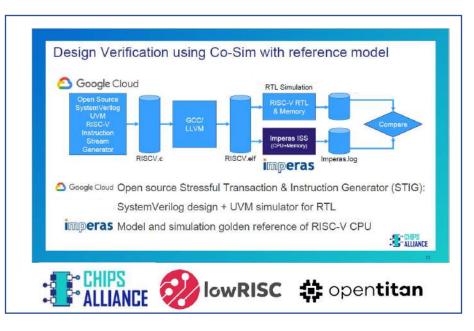

#### #2: Entry Level DV: post-sim trace-compare (use e.g. riscvOVPsimPlus ISS from OVPworld)

Imperas riscvOVPsimPlus Reference Simulator

Page 26

#### Process

• use random generator (ISG) to create tests

- during simulation of ISS write trace log file

- during simulation of RTL write trace log file

- at the end of both runs, run logs through compare program to see differences / failures

- ISS: riscvOVPsimPlus includes Trace and GDB interface

- Free ISS: <u>https://www.ovpworld.org/riscvOVPsimPlus</u>

- ISG: riscv-dv from Google Cloud / Chips Alliance

- Free ISG: <u>https://github.com/google/riscv-dv</u>

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

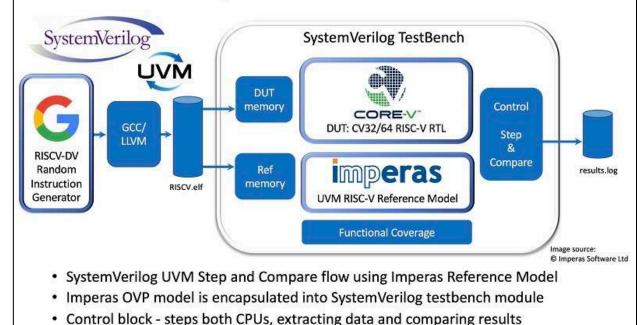

# #3: Industrial Quality Sync DV (sync-lock-step-compare)

Example flow:

Tandem lockstep run – both reference and DUT run together in lock step

- Not very complex to obtain, set up

- Compare PC, CSRs, GPRs, other internal state instruction by instruction

- No requirement on data saving

- No requirement on known good results in test

- Will not work for async events and control flow ,

... it is all about the data flow

- [OpenHW evolved into using async see later slides]

Coverage Driven Verification of OpenHW CORE-V Processors with Imperas RISC-V Golden Reference Model

1<sup>st</sup> Generation OpenHW flow (1H2020)

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

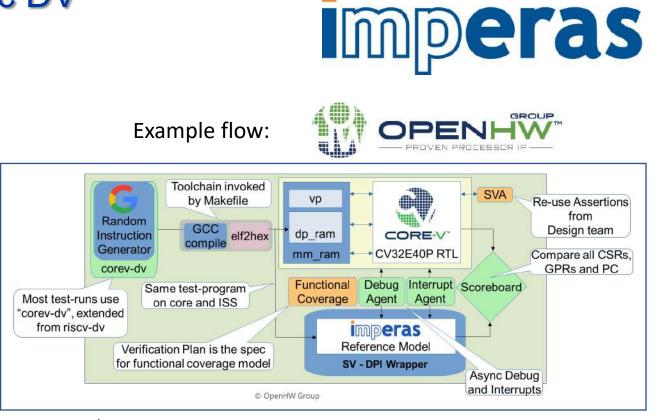

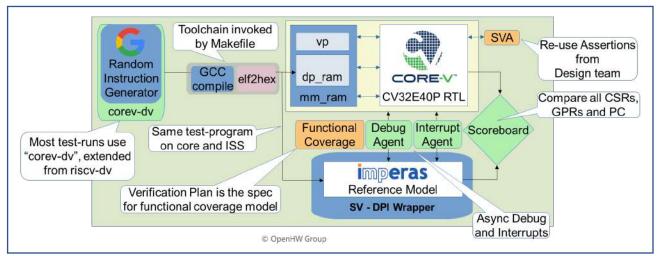

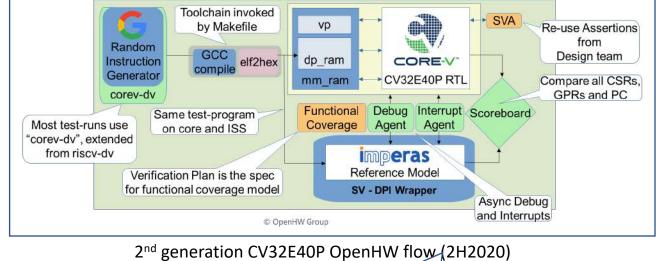

# #4: Industrial Highest Quality Async DV (async-lock-step-compare)

- Builds on & extends Industrial Quality sync-lock-step-compare DV

- Adds focus on async capabilities

- Depending on design this can include: OoO, MP, debug mode, interrupts, multi-issue, ...

- Example SystemVerilog Components

- tracer: Reports instructions for checking and register writebacks

- step\_and\_compare: Manages the reference model and checks functionality

- interrupt\_assert: Properties for interrupt coverage/checking

- debug\_assert: Properties for debug coverage/checking

- Typically hard, complex, and expensive to get working

- Challenge is extracting async info from microarchitecture RTL pipeline

- See latest developments with RVVI and ImperasDV

#### 2<sup>nd</sup> generation CV32E40P OpenHW flow (2H2020) (Imperas model encapsulated in SystemVerilog)

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

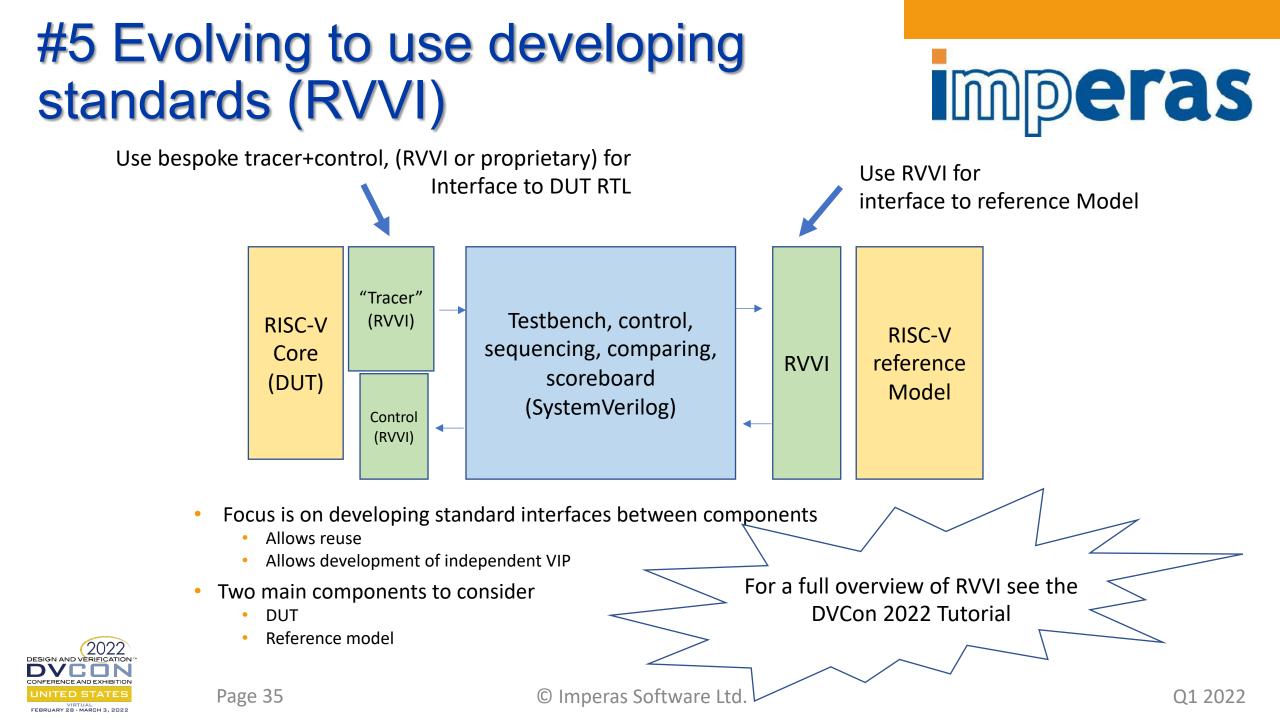

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Digression into why we need standards...

- Components of RISC-V CPU DV environment

# Challenges moving forward – the need for standards

- There are many different components needed:

- DUT & its encapsulation

- 'tracer' information

- Control

- Reference model & its encapsulation

- Configuration

- Comparisons

- Synchronization

- Asynchronous operations

- Control

- Functional coverage measurement & assertions

- Test bench

- Configuration

- Overall control

- Scoreboarding

- Reporting / Logging

- Tests (directed or generated)

- Program linker scripts and binary file reader

- And each component has different interfaces and requirements on the interfaces

Imperas

2<sup>nd</sup> generation CV32E40P OpenHW flow (2H2020)

#### Challenges moving forward – the need for standards

- There are many different components needed:

- **DUT & its encapsulation**

- 'tracer' information

- Control

- Reference model & its encapsulation

- Configuration

- Comparisons

- Synchronization

- Asynchronous operations

- Control

- Functional coverage measurement & assertions

- Test bench

- Configuration

- **Overall control**

- Scoreboarding

- Reporting / Logging

- Tests (directed or generated)

- Program linker scripts and binary file reader

- And each component has different interfaces and ٠ requirements on the interfaces

It would be a disaster for RISC-V if every design team had to re-invent everything...

© Imperas Software Ltd

DESIGN AND VERIFICATION VIRTUAL FEBRUARY 28 - MARCH 3, 2022

Page 34

## Key component is Reference Model

- RISC-V is highly configurable & extendable

- 200... Questions ?

- So it can get a little .... complicated

#### Example reference model: Imperas

#### http://www.imperas.com/riscv

- Imperas provides full RISC-V Specification envelope model

- Industrial quality model /simulator of RISC-V processors for use in compliance, verification and test development

- Complete, fully functional, configurable model / simulator

- All 32bit and 64bit features of ratified User and Privilege RISC-V specs

- Unprivileged versions 2.2, 20191213

- Privilege versions 1.10, 1.11, 1.12

- Vector extension, versions 0.7.1, 0.8, 0.9, 1.0

- Bit Manipulation extension, versions 0.91, 0.92. 0.93, 1.0.0

- Hypervisor version 0.6.1, 1.0.0

- K-Crypto Scalar version 0.7.1, 1.0.0

- Debug versions 0.13.2, 0.14, 1.0.0

- P DSP/SIMD versions 0.5.2, 0.9.6

- Zicbom, Zicbop, Zicboz, Zmmul, Zfh, Zfinx, Zce

- Svnapot, Svpbmt, Svinval, Smstaten, Smepmp, ...

- Model source included under Apache 2.0 open source license

- Used as reference by :

- Mellanox/Nvidia, Seagate, NSITEXE/Denso, Google Cloud, Chips Alliance, IowRISC, OpenHW Group, Andes, Valtrix, SiFive, Codasip, MIPS, Nagra/Kudelski, Silicon Labs, RISC-V Compliance Working Group, ...

#### Imperas is used as RISC-V Golden Reference Model

Page 37

© Imperas Software Ltd.

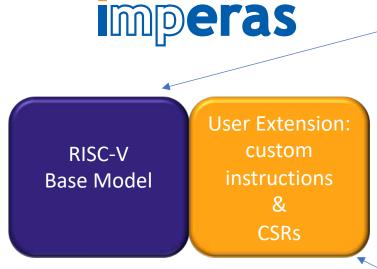

#### Imperas Model extensibility

- Separate source files and no duplication to ensure easy maintenance

- Imperas or user can develop the extension

- User extension source can be proprietary

Page 38

Imperas develops and maintains base model

- Base model implements RISC-V specification in full

- Fully configurable to select which ISA extensions

- Fully configurable to select which version of each ISA extension

- Updated very regularly as ISA extension specification versions change

- Fully configurable for all RISC-V specification options

- e.g. implemented optional CSRs, read only or read/write bits etc...

Imperas provides methodology to easily extend base model

- Templates to add new instructions

- Code fragments for adding functionality

- 100+ page user guide/reference manual with many examples

- Includes example extended processor model

## Imperas model is architected for easy extension & maintenance

© Imperas Software Ltd.

## Imperas News at DVCon 2022

# **I**mperas

The leader in simulation solutions for RISC-V

Imperas announces RISC-V Physical Memory Protection (PMP) Architectural Validation test suite for high quality security applications Imperas RISC-V Verification Solutions https://www.imperas.com/imperasdv

The full press release is available at the Imperas virtual booth at DVCon 2022

## Imperas News at DVCon 2022

01 2022

#### Conclusions

- The open standard ISA of RISC-V offers many design freedoms

- Many standard extensions and configuration options plus custom instructions

- The key verification requirements are to detect discrepancies with efficient debug

- The open standard RVVI offers a framework for verification reuse with support for both opensource and commercial tools

- RISC-V Verification Interface

- https://github.com/riscv-verification/RVVI

- Lockstep / Compare is by far the best and most efficient approach (industry 'gold standard')

- https://www.imperas.com/imperasdv

- For more detail see the full tutorial

- 'Introduction to the 5 levels of RISC-V Processor Verification'

- DVCon 2022 Recording from Monday February 28th 9:00-11:00am PST

## **Thank You!**

KevinM@imperas.com

www.imperas.com

www.imperas.com/ImperasDV

www.OVPworld.org

## Imperas at DVCon 2022

- Tutorial: 'Introduction to the 5 levels of RISC-V Processor Verification'

- Simon Davidmann and Lee Moore Imperas Software

- Monday February 28th 9:00-11:00am PST

- Presentation: 'Introduction to RISC-V CPU design verification'

- Kevin McDermott Imperas Software

- Tuesday March 1st 12:30-1:00 pm PST

- Presentation: 'Imperas RISC-V Design Verification solutions'

- Larry Lapides Imperas Software

- Tuesday March 1st 1:00-1:30pm PST