#### Methodology for Implementation of Custom Instructions in RISC-V Architecture

Lee Moore, Simon Davidmann, <u>Larry Lapides</u>

Imperas Software Ltd.

and

Carl Shaw

Cerberus Security Labs

### Agenda

mperas

Who is adopting RISC-V and why...

### There are and will be many different RISC-V CPU developers:

- There are and will be many different RISC-V CPU developers:

- Develop internal cores for SoCs

- e.g. Nvidia, ...

- Deliver RTL IP as a business (like Arm, MIPS, just for RISC-V)

- e.g. Andes, Codasip, Syntacore, Incore, ...

- Develop for internal use but make available as open source

- e.g. Western Digital, ...

- Develop and use open source as a business opportunity

- e.g. SiFive, ...

- Purchase processor IP and develop semiconductor products

- e.g. Microsemi SoC FPGAs, ...

- Download and use open source RTL in their products

- e.g. Google, ...

•

### RISC-V CPU Adopters: (above & below the line)

New architectures (ML, IoT), arrays of processors, custom features, high performance, feature control (efficiency), large SoC design, architecture innovation, ...

Key requirement: 'freedom to innovate'

Researchers, education, open source community, freely available, no license cost or restriction, ...

Key requirement: 'free'

# Many (above the line) adopters of RISC-V want to add their own custom extension instructions

- Traditional ISA choice has been hard if you want to add your own custom processor instructions to an ISA

- RISC-V as an open standard has specific regions of instruction decode space specifically allocated for users to add their own instructions

- Challenges

- How to choose the processor IP starting point

- How to add instructions to processor RTL

- How to verify the complete RTL

- How to evaluate effectiveness and performance gains of new instructions

- How to enable software development utilizing the new instructions

#### Agenda

- Who is adopting RISC-V and why...

- Adding custom instructions to RISC-V processors

# Processor IP and Custom Instructions

- Processor IP vendors

- Provide high quality RTL

- Provide methodology for adding custom instructions

- How to verify custom instructions?

- Open source RTL

- Should be high quality

- How has open source been verified?

- Add custom instructions by modifying RTL

- How to verify custom instructions?

- Roll-your-own

- Starting from scratch on RTL requires significant implementation expertise

- Just build in custom instructions from beginning

- How to verify complete processor implementation?

#### Key Challenge of Optimizing Custom Instructions Requires New Methodology, Tools

- How to choose the processor IP starting point

- How to add instructions to processor RTL

- How to verify the complete RTL

- How to evaluate effectiveness and performance gains of new instructions

- How to enable software development utilizing the new instructions

- ➤ Extend instruction accurate simulation tools and models to support analysis and optimization of custom instructions

### Agenda

- Who is adopting RISC-V and why...

- Adding custom instructions to RISC-V processors

- Custom instruction optimization flow

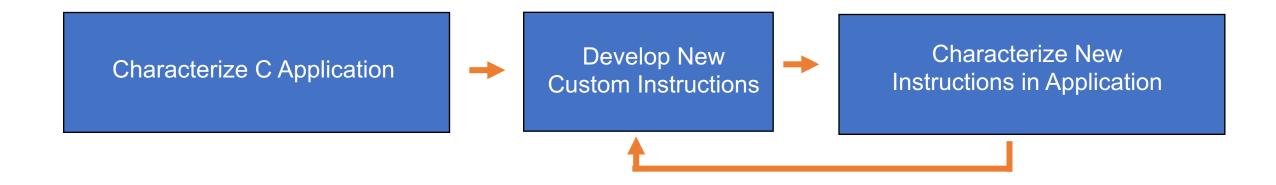

## Custom Instruction Optimization Flow

- Show the flow used when designing new instructions to improve performance of applications running on a RISC-V processor

- Allows evaluation and firming up of the instructions

- Gets to the specification of the instructions needed to be implemented in RTL

- Introduce the technologies & tools needed for each stage

- Application software used for this walk-through is a character stream encoder, based on ChaCha20 encryption algorithm

- Instruction Extensions to RISC-V courtesy of Cerberus Security Laboratories Ltd

- https://cerberus-laboratories.com

Characterize C Application

Characterize C Application

Develop New Custom Instructions

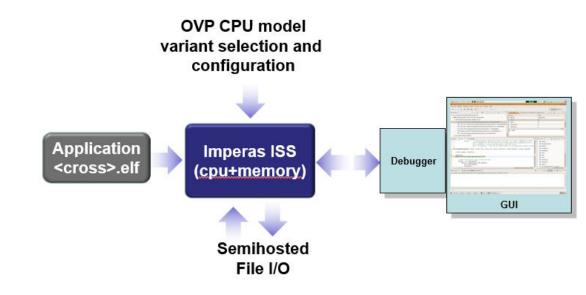

# The first thing needed is a simulator – think ISS, however ...

- Simulator and model need to have ability to extend to allow custom instructions and new tools

- Ease of use also important

- Need to have a business-friendly open source license

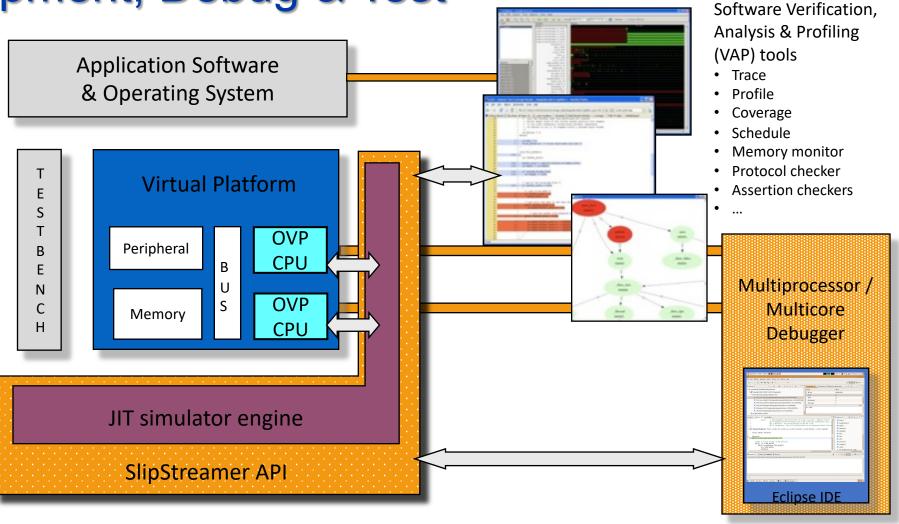

Imperas Tools for Embedded Software Development, Debug & Test

**Imperas**

#### Characterize C Application

- Instruction Accurate Simulation

- Trace / Debug

- Timing Simulation

- Function Timing / Profiling

### Instruction Accurate simulation

of C application

- Cross compiled C application targeting RV32IM

- Character stream encoder, with ChaCha20 encryption algorithm

- IA simulation

- Imperas RISC-V ISS with configurable model of RISC-V specification selecting RV32IM

- Semihosting

- Enables bare metal application to very simply access host I/O

- >runs fast

- Over 1 billion instructions a second (standard PC)

- Linux and Windows supported host OS

```

test_c.c 23

unsigned int processLine(unsigned int res, unsigned int word) {

res = grl c(res, word);

res = qr2_c(res, word)

res = gr2 c(res, word);

res = gr3 c(res, word);

res = qr4_c(res, word);

return res;

int main(void) {

const char *customData = "application/custom.data";

FILE *fp = fopen(customData, "r");

if (fp) {

unsigned int res = 0x84772366;

unsigned int word;

unsigned int cnt=0;

unsigned int iter=0;

while (iter++ < 16) {

while (fread(&word, sizeof(unsigned int), 1, fp)) {

res = processLine(res, word);

CpuManagerMulti (32-Bit) v99999999 Open Virtual Platform simulator from www.IMPERAS.com.

Copyright (c) 2005-2018 Imperas Software Ltd. Contains Imperas Proprietary Information.

icensed Software, All Rights Reserved.

fclose(fp)

CpuManagerMulti started: Thu Aug 23 11:19:21 2018

printf("RES = %08

0x00000000 0x00010000 0x00010000 0x000173c8 0x000173c8 R-E

0x000173c8 0x000283c8 0x000283c8 0x000009c0 0x000000a24 RM- 1000

nFo (OR_OF) Target 'iss/cpu0' has object file read from 'application/exception,RISCV32,elf'

Offset VirtAddr PhysAddr FileSiz MemSiz Flags Alig

Info CPU 'iss/cpu0' STATISTICS

Final program counter: 0x100ac

Simulated tipe

Elapsed time

: 11,31x faster

CpuManagerMulti finished: Thu Aug 23 11:19:22 2018

```

# Cycle Approximate simulation Capplication

- Same C application

- IA simulation + timing Estimation (IA+E)

- Includes annotated timing estimation for RV32IM processor

- Same simulation data results, different timing as now counting cycles

- Shows how long algorithm will take to execute

- > Extends simulated time

- Was 12.89 secs now takes 16.59 secs

```

CpuManagerMulti (32-Bit) v99999999 Open Virtual Platform simulator from www.IMPERAS.com.

Copyright (c) 2005-2018 Imperas Software Ltd. Contains Imperas Proprietary Information.

Licensed Software, All Rights Reserved.

Visit www.IMPERAS.com for multicore debug, verification and analysis solutions.

CpuManagerMulti started: Thu Aug 23 11:27:16 2018

Info (OR_OF) Target 'iss/cpu0' has object file read from 'application/test_c.RISCV32.elf'

Info (OR_PH) Program Headers:

VirtAddr PhysAddr FileSiz MemSiz

0x00000000 0x00010000 0x00010000 0x000173c8 0x000173c8 R-E 1000

0x000173c8 0x000293c8 0x000293c8 0x000009c0 0x00000a24 RM-

Info (OR_OF) Target 'iss/cpu0' has object file read from 'application/exception.RISCV32.elf'

VirtAddr PhysAddr FileSiz MenSiz

0x00001000 0x00000000 0x00000000 0x0000000c 0x0000000c R-E

Info (CMD_CC) calling 'iss/cpu0/exTT/cpucycles'

(CPUEST_CMB) iss/cpu0; cpucycles on; time stretch enabled

: riscv (RV32IM)

: 100

Final program counter : 0x100ac

Simulated instructions: 1,289,380,976

: 16,59 seconds

8,58 seconds

CpuManagerMulti finished: Thu Aug 23 11:27:25 2018

CpuManagerMulti (32-Bit) v99999999 Open Virtual Platform simulator from www.IMPERAS.com.

Visit www.IMPERAS.com for multicore debug, verification and analysis solutions.

Info (CPUEST_RSLT) Estimated execution time 16.59 seconds, clock cycles 1,659,204,454

```

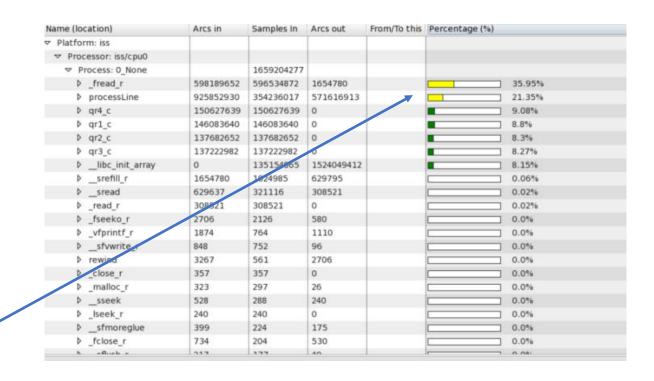

- Same C application

- IA+E simulation

- Sampled profiling with call stack analysis

- Shows proportion of time spent in each application function

- >21.35% spent in processLine

#### Characterize C Application

- Instruction Accurate Simulation

- Trace / Debug

- Timing Simulation

- Function Timing / Profiling

- Design Instructions

- Add to Application

- Add to Model

- Add Timing

# Add custom instructions to application

- Inline assembly using new instructions replacing C code

- 4 new instructions

- Cross Compile using standard tool

- Run on IA simulator

- Unimplemented instruction exception

- As the instructions have not yet been added to the simulator model

```

// Custom instruction test for Chacha20

#include <stdio.b>

unsigned int processLine(unsigned int input, unsigned int word) {

unsigned int res = input;

asm __volatile__("mv x10, %0" :: "r"(res));

asm __volatile__("mv x11, %0" :: "r"(word));

asm __volatile__(".word 0x00850508\n" ::: "x10");

asm __volatile__(".word 0x00851508\n" ::: "x10");

asm __volatile__(".word 0x00B52508\n" ::: "x10");

asm __volatile__(".word 0x00853508\n" ::: "x10");

asm __volatile__(".word 0x00B50508\n" ::: "x10");

// QR1

asm __volatile__(".word 0x00B5150B\n" ::: "x10");

asm __volatile__(".word 0x00B5250B\n" ::: "x10");

// QR3

asm __volatile__(".word 0x00B5350B\n" ::: "x10");

asm __volatile__("mv %0,x10" : "=r"(res));

return res;

CpuManagerMulti (32-Bit) v99999999 Open Virtual Platform simulator from www.IMPERAS.com,

int maiCopyright (c) 2005-2018 Imperas Software Ltd. Contains Imperas Proprietary Information.

icensed Software, All Rights Reserved.

Visit www.IMPERAS.com for multicore debug, verification and analysis solutions.

CouManagerMulti started: Thu Aug 23 11:34:51 2018

0x00000000 0x00010000 0x00010000 0x00017270 0x00017270 R-E 1000

0x00017270 0x00028270 0x00028270 0x000009c0 0x00000a24 RM-

(OR_OF) Target 'iss/cpu0' has object file read from 'application/exception_RISCV32.elf'

iss/cpu0' 0x00010248 00b5050b custom1: Illegal instruction - extension X (non-standard extensions present) absent or inactive

: riscv (RV321M)

: 100

Final program counter: 0x102e4

: run too short for meaningful result

Info SIMULATION TIME STATISTICS

Simulated time

Sustem time

: 0.00 seconds

Elapsed time

CpuManagerMulti finished: Thu Aug 23 11:34:51 2018

```

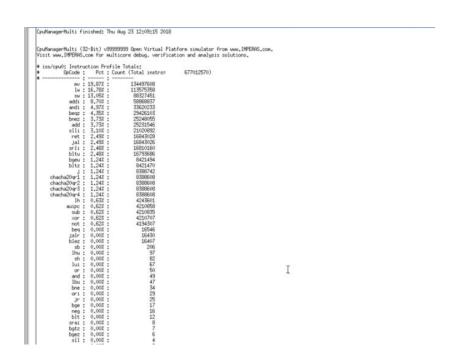

## Add custom instructions to model

- Use standard Open Virtual Platforms (OVP) instruction modeling APIs to add new instructions (and optional state) as new extension library

- Easy to extend decode table, add efficient behavioral JIT code

- Optionally can call directly into user's provided C function of behavior

- Compile and link model extension library

- Simulate IA with ISS plus standard model extended with new library

- Instruction count and simulated time have reduced (IA)

```

// Create the RISCV decode table

static vmidDecodeTableP createDecodeTable(void)

vmidDecodeTableP table = vmidNewDecodeTable(RISCV INSTR BITS, RISCV EIT LAST);

// Emit code implementing exchange instruction

// R-Type instruction in custom-0 encoding space:

// opcode [6:0] = 00 010 11

static void emitChaCha20(

// funct3[14:12] = 0,1,2,3 (QR1-4)

vmiProcessorP processor,

// funct7[31:25] = 0000000

vmiosObjectP object,

// rs1[19:15]

Uns32

instruction,

// rs2[24:20]

Uns32

rotl

// rd[11:7]

// handle custom instruction

// extract instruction fields

DECODE ENTRY(0, CHACHA20QR1, "|0000000......000.....0001011|");

Uns32 rd = RD(instruction);

DECODE ENTRY(0, CHACHA20QR2, "|00000000......001....0001011|");

Uns32 rs1 = RS1(instruction);

DECODE_ENTRY(0, CHACHA20QR3, "|00000000......010.....0001011|");

Uns32 rs2 = RS2(instruction):

DECODE ENTRY(0, CHACHA20QR4, "[00000000......011....0001011]");

vmiReg reg rs1 = vmimtGetExtReg(processor, &object->rs1);

return table;

vmiReg reg_rs2 = vmimtGetExtReg(processor, &object->rs2);

vmiReg reg tmp = vmimtGetExtTemp(processor, &object->tmp);

vmimtGetR(processor, RISCV_REG_BITS, reg_rs1, object->riscvRegs[rs1]);

vmimtGetR(processor, RISCV_REG_BITS, reg_rs2, object->riscvRegs[rs2]);

opyright (c) 2005-2018 Imperas Software Ltd. Contains Imperas Proprietary Information.

vmimtBinopRRR(32, vmi_XOR, reg_tmp, reg_rs1, reg_rs2, 0);

icensed Software, All Rights Reserved.

isit www.IMPERAS.com for multicore debug. verification and analysis solutions

vmimtBinopRC(32, vmi ROL, reg tmp, rotl, θ);

puManagerMulti started: Thu Aug 23 11:41:32 201

vmimtSetR(processor, RISCV REG BITS, object->riscvRegs[rd], reg tmp);

Offset VirtAddr PhysAddr FileSiz MemSiz Flags Align

0x00000000 0x00010000 0x00010000 0x00017270 0x00017270 R-E 1000

0v00017270 0v00028270 0v00028270 0v000009+0 0v00000a24 RM-

$IMPERAS_VLNV/riscv.ovpworld.org/semihosting/riscv32Newlib/1.0/model

instructionExtensionLib

nfo CPU 'iss/cpu0' STATISTICS

Final program counter: 0x100ac

Simulated instructions: 677,012,570

Simulated MIPS: 1301.9

NFO SIMULATION TIME STATISTICS

Simulated time

: 0,50 seconds

: 0.02 seconds

: 0.53 seconds

: 12.81x faster

Elapsed time

puManagerMulti finished: Thu Aug 23 11:41:33 2018

```

### Cycle Approximate simulation including custom instructions

- IA simulation + timing annotation + custom instructions

- Includes timing estimation for RV32IM processor

- Need to add timing estimation for new custom instructions

- Simulate using C code application with inline assembler of custom extensions

- IA simulator + timing tool + custom extension instruction library

- See estimated improvement in throughput of application on new processor

- ➤ Was (IA) 6.77 secs now (CA) 9.21 secs

```

customChaCha20.c

case IC mdu mul :

cycles = 5;

// Specify cycles for instruction group

break;

case IC mdu div : {

cycles = 16;

// Specify cycles for instruction group

break:

case IC_custom : {

// chacha20gr1-chacha20gr4 group same cycles

// Specify cycles for instruction group

cycles = 2;

break:

VMI ABORT("Invalid instructionClassE value %d (%s)\n", iClass, instrClassName(iClass));

if (runtimeCB) { // division run-time callback

emitCycleEstimation(processor,object,thisPC,regSource1,regSource2,mduMode,iClass,runtimeCB)

addCycleCount(object, thisPC, cycles, iClass);

Info CPU 'iss/cpu0' STATISTICS

Simulated instructions: 677,012,570

Simulated time

: 0,20 seconds

buManagerMulti (32-Bit) v99999999 Open Virtual Platform simulator from www.lMPERGS.com

Info (CPUEST_RSLT) Estimated execution time 9,21 seconds, clock cucles 921,006,928

Use script lastRun.sh to re-run with current settings

```

- Simulator has many trace features built in

- See new custom instructions in trace disassembly

- Can select when/where to turn trace on/off

- Very efficient tracing

```

CpuManagerMulti started; Thu Aug 23 12:02:30 2018

Info (OR_OF) Target 'iss/cpu0' has object file read from 'application/test_custom_RISCV32.elf'

Info (OR_PH) Program Headers;

Info (OR_PH) Type

VirtAddr PhysAddr FileSiz MemSiz Flags Align

Info (OR PD) LOAD

0x00000000 0x00010000 0x00010000 0x00017270 0x00017270 R-E 1000

0x00017270 0x00028270 0x00028270 0x000009c0 0x00000a24 RM-

Info (OR_OF) Target 'iss/cpu0' has object file read from 'application/exception.RISCV32.elf'

Info (OR_PH) Program Headers;

VirtAddr PhysAddr FileSiz MemSiz

0x00001000 0x00000000 0x00000000 0x0000000c 0x0000000c R-E 1000

Info 1330: 'iss/cpu0', 0x0000000000010228(processLine+c): fca42e23 sw

a0,-36(s0)

Info 1331: 'iss/cpu0', 0x000000000001022c(processLine+10): fcb42c23 sw

Info 1332: 'iss/cpu0', 0x000000000010230(processLine+14): fdc42783 lw

a5,-36(s0)

Info a5 a730c140 -> 84772366

Info 1333: 'iss/cpu0', 0x0000000000010234(processLine+18): fef42623 sw

a5,-20(s0)

nt- 1334: 'iss/cpu0', 0x000000000010238(processLine+1c): fec42783 lw

iss/cpu0', 0x00000000001023c(processLine+20): 00078513 mv

Info 1336; 'iss/cpus' 0x0000000000010240(processLine+24); fd842783 lw

a5,-40(s0)

Info a5 84772366 -> a730ca

Info 1337: 'iss/cpu0', 0x00000000

essLine+2c); chacha20gr1 a0,a0,a1

Info 1338: 'iss/cpu0', 0x0000000000010248(pri

Info a0 84772366 -> e2262347

Info 1339: 'iss/cpu0', 0x00000000001024c(processLine+30): chacha20gr2 a0,a0,a1

Info a0 e2262347 -> 5e207451

Info 1340; 'iss/cpu0', 0x0000000000010250(processLine+34); chacha20gr3 a0,a0,a1

Info a0 6e207451 -> 10b511c9

Info 1341: 'iss/cpu0', 0x0000000000010254(processLine+38): chacha20gr4 a0,a0,a1

Info a0 10b511c9 -> c2e844db

Info 1342; 'iss/cpu0', 0x0000000000010258(processLine+3c); chacha20gr1 a0,a0,a1

Info a0 c2e844db -> 859b65d8

Info 1343: 'iss/cpu0', 0x000000000001025c(processLine+40): chacha20gr2 a0,a0,a1

Info a0 859b65d8 -> ba49822a

Info 1344; 'iss/cpu0', 0x0000000000010260(processLine+44); chacha20gr3 a0.a0.a1

Info a0 ba49822a -> 79436a1d

Info 1345: 'iss/cpu0', 0x0000000000010264(processLine+48): chacha20gr4 a0,a0,a1

nfo a0 79436a1d -> 39d5aeef

Info 1346: 'iss/cpu0', 0x0000000000010268(processLine+4c): 00050793 mv

Info a5 a730c140 -> 39d5aeef

Info 1347; 'iss/cpu0', 0x000000000001026c(processLine+50); fef42623 sw

Info 1348; 'iss/cpu0', 0x0000000000010270(processLine+54); fec42783 lw

a5,-20(s0)

Info 1349: 'iss/cpu0', 0x0000000000010274(processLine+58): 00078513 mv

RES = 84772366

Info CPU 'iss/cpu0' STATISTICS

: riscy (RV32IM)

Nominal MIPS

: 100

Final program counter : 0x100ac

Simulated instructions: 677,012,570

Simulated MIPS

```

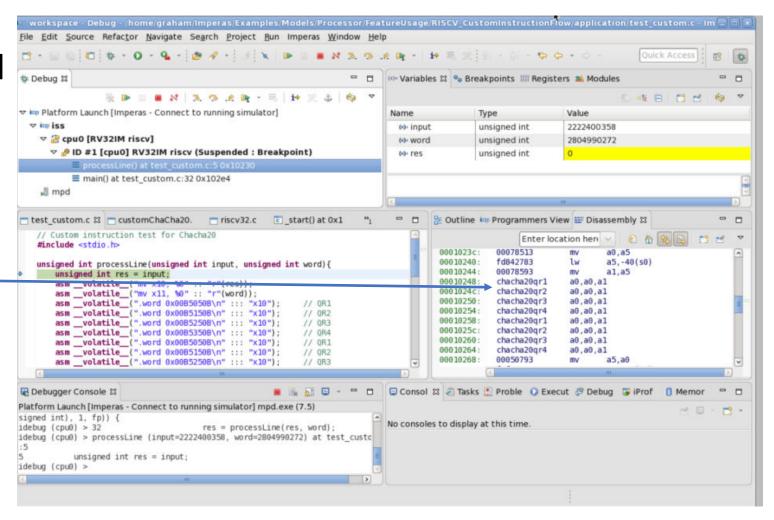

#### Debug custom instructions

- Imperas MPD is Eclipse based source code debug tool

- Can debug using source line or instruction level

- See new custom instructions and any new additional state registers

# Function Profile custom instructions application

- IA simulation + timing annotation + custom instructions with sampled profiling

- >Shows where slowest function is

- Now much faster...

- Shows benefits of using custom instructions

- processLine was 21.35% now 16.3%

| Name (location)           | Arcs in   | Samples In | Arcs out  | From/To this | Percentage (%) | ~ |

|---------------------------|-----------|------------|-----------|--------------|----------------|---|

| ♥ Platform: iss           |           |            | 1         |              |                |   |

| ▽ Processor: iss/cpu0     |           |            |           |              |                |   |

| ♥ Process: 0_None         |           | 921006649  |           |              |                |   |

| ▷ _fread_r                | 635365939 | 633628269  | 1737670   |              | 68.8%          |   |

| Dibc_init_array           | 0         | 150138664  | 770867985 |              | 16.3%          |   |

| ▶ processLine             | 135494635 | 135494635  | 0         |              | 14.71%         |   |

| ▶srefill_r                | 1737670   | 1066083    | 671587    |              | 0.12%          |   |

| ♪ _read_r                 | 340125    | 340125     | 0         |              | 0.04%          |   |

| ▶ _sread                  | 671429    | 331304     | 340125    |              | 0.04%          |   |

| ♪ _fseeko_r               | 3849      | 3269       | 580       |              | 0.0%           |   |

| <pre>Dsfvwrite_r</pre>    | 784       | 688        | 96        |              | 0.0%           |   |

| Þ _sflush_r               | 599       | 559        | 40        |              | 0.0%           |   |

| <pre>D _vfprintf_r</pre>  | 1492      | 446        | 1046      |              | 0.0%           |   |

| ▶ rewind                  | 4153      | 304        | 3849      |              | 0.0%           |   |

| ▶ _malloc_r               | 323       | 297        | 26        |              | 0.0%           |   |

| ♪ _sseek                  | 528       | 288        | 240       |              | 0.0%           |   |

| <pre>Þ _lseek_r</pre>     | 240       | 240        | 0         |              | 0.0%           |   |

| ▶ _sfmoreglue             | 399       | 224        | 175       |              | 0.0%           |   |

| ▶ _fclose_r               | 811       | 204        | 607       |              | 0.0%           |   |

|                           | 146       | 146        | 0         |              | 0.0%           |   |

| <pre>p _fwalk_reent</pre> | 790       | 106        | 684       |              | 0.0%           |   |

| ▷ _sfp                    | 641       | 96         | 545       |              | 0.0%           |   |

| ▶ smakebuf r              | 316       | 78         | 238       |              | 0.0%           |   |

# Basic Block (BB) Profile custom instructions application

- IA simulation + timing annotation + custom instructions with detailed BB profiling

- Shows where expensive instruction sequences are

- Allows understanding of instruction performance

- Useful for Compiler teams

- Useful for Hardware teams

```

BbProfile_c.txt

BB@0x000102ac:0x000102d0 executed 5758080

0x000102ac(qr1 c+0x0): ff010113 addi

sp, sp, -16

0x000102b0(qr1 c+0x4): 00812623 sw

s0,12(sp)

0x000102b4(qr1 c+0x8): 01010413 addi

s0, sp, 16

0x000102b8(qr1 c+0x12): 00b545b3 xor

a1, a0, a1

0x000102bc(qr1 c+0x16): 01059513 slli

a0, a1, 0x10

0x000102c0(qr1 c+0x20): 0105d593 srli

a1, a1, 0x10

a0, a1, a0

0x000102c4(qr1 c+0x24): 00a5e533 or

0x000102c8(qr1 c+0x28): 00c12403 lw

s0,12(sp)

0x000102cc(qr1 c+0x32): 01010113 addi

sp, sp, 16

0x000102d0(qr1 c+0x36): 00008067 ret

12

BB@0x000102d4:0x000102f8 executed 5758080 times:

0x000102d4(qr2 c+0x0): ff010113 addi

sp, sp, -16

15

0x000102d8(qr2 c+0x4): 00812623 sw

s0,12(sp)

0x000102dc(qr2 c+0x8): 01010413 addi

s0, sp, 16

0x000102e0(qr2 c+0x12): 00b545b3 xor

a1,a0,a1

0x000102e4(qr2 c+0x16): 00c59513 slli

a0, a1, 0xc

0x000102e8(qr2 c+0x20): 0145d593 srli

a1, a1, 0x14

a0, a1, a0

0x000102ec(qr2 c+0x24): 00a5e533 or

0x000102f0(qr2 c+0x28): 00c12403 lw

s0,12(sp)

0x000102f4(qr2 c+0x32): 01010113 addi

sp, sp, 16

0x000102f8(qr2 c+0x36): 00008067 ret

BB@0x000102fc:0x00010320 executed 5758080

0x000102fc(qr3 c+0x0): ff010113 addi

sp, sp, -16

0x00010300(qr3 c+0x4): 00812623 sw

s0,12(sp)

0x00010304(qr3 c+0x8): 01010413 addi

s0, sp, 16

0x00010308(qr3 c+0x12): 00b545b3 xor

a1, a0, a1

0x0001030c(qr3 c+0x16): 00859513 slli

a0, a1, 0x8

0x00010310(qr3 c+0x20): 0185d593 srli

a1,a1,0x18

Windows (CR LF) UTF-8

ength: 4,975 Ln:1 Col:1 Sel:0 | 0

```

## mperas

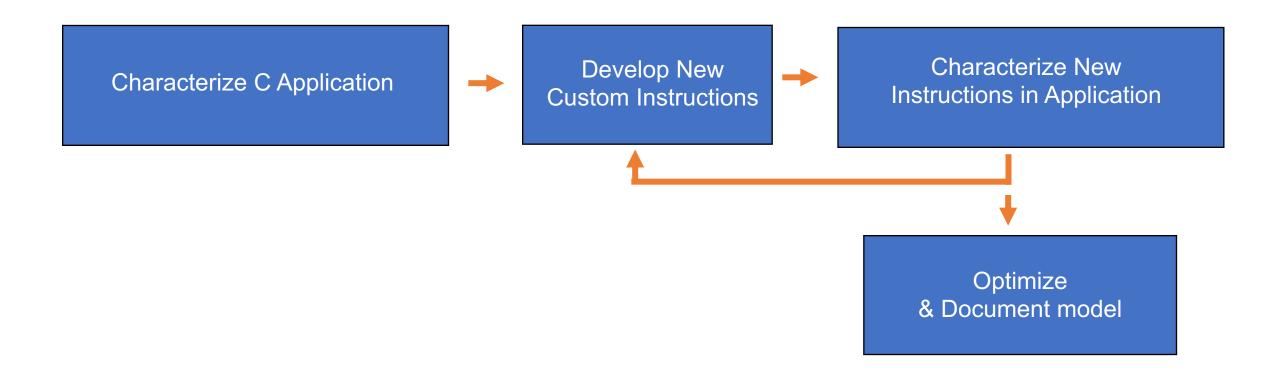

#### Characterize C Application

- Instruction Accurate Simulation

- Trace / Debug

- Timing Simulation

- Function Timing / Profiling

#### Develop New Custom Instructions

- Design Instructions

- Add to Application

- Add to Model

- Add Timing

#### Characterize New Instructions in Application

- Instruction Accurate Simulation

- Trace / Debug

- Timing Simulation

- Function Timing / Profiling

## mperas

#### Characterize C Application

- Instruction Accurate Simulation

- Trace / Debug

- Timing Simulation

- Function Timing / Profiling

#### Develop New Custom Instructions

- Design Instructions

- Add to Application

- Add to Model

- Add Timing

#### Characterize New Instructions in Application

- Instruction Accurate Simulation

- Trace / Debug

- Timing Simulation

- Function Timing / Profiling

#### Optimize & Document model

- Instruction Coverage

- Line Coverage

- Instruction Performance

- Generate PDF model doc

- Model source line coverage

- To see how completely the tests exercise the model

| Name                 | Total Lines | Instrumente | Executed Lir | Coverage %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

|----------------------|-------------|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| ✓ Summary            | 16,900      | 4,411       | 2,834        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64.25% |

| customChaCha20.c     | 374         | 87          | 42           | i de la constanti de la consta | 48.28% |

| riscvBus.c           | 175         | 46          | 1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.17%  |

| riscvCSR.c           | 2,573       | 758         | 549          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72.43% |

| riscvConfigList.c    | 70          | 2           | 0            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.0%   |

| riscvDebug.c         | 527         | 167         | 72           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43.11% |

| riscvDecode.c        | 1,599       | 360         | 164          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45.56% |

| riscvDisassemble.c   | 514         | 185         | 185          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100.0% |

| riscvDoc.c           | 725         | 143         | 30           | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20.98% |

| riscvExceptions.c    | 1,408       | 420         | 317          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75.48% |

| riscvInfo.c          | 83          | 3           | 0            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.0%   |

| riscvMain.c          | 383         | 147         | 25           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17.01% |

| riscvMorph.c         | 2,887       | 1,032       | 776          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75.19% |

| riscvParameters.c    | 589         | 145         | 9            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.21%  |

| riscvRegisterTypes.h | 115         | 10          | 6            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60.0%  |

| riscvSemiHost.c      | 44          | 6           | 3            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50.0%  |

| riscvStructure.h     | 204         | 4           | 2            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50.0%  |

| riscvUtils.c         | 493         | 122         | 45           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36.89% |

| riscvVM.c            | 2,695       | 770         | 608          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78.96% |

| vmiMt.h              | 1,442       | 4           | 0            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.0%   |

```

test_c.c test_custom.c customChaCha20.c triscv32.c test_custom.c

// Emit code implementing exchange instruction

static void emitChaCha20(

vmiProcessorP processor,

vmiosObjectP object,

Uns32

instruction,

Uns32

// extract instruction fields

Uns32 rs1 = RS1(instruction)

Uns32 rs2 = RS2(instruction)

vmiReg reg_rs1 = vmimtGetExtReg(processor, &object->rs1)

vmiReg reg_rs2 = vmimtGetExtReg(r

line executed 16 times

vmiReg reg_tmp = vmimtGetExtTemp

vmimtGetR(processor, RISCV_REG_BITS, reg_rs1, object->riscvRegs[rs1]);

vmimtGetR(processor, RISCV REG BITS, reg rs2, object->riscvRegs[rs2]);

vmimtBinopRRR(32, vmi_XOR, reg_tmp, reg_rs1, reg_rs2, 0);

```

- Custom instruction coverage

- To see that there are tests for new instructions

- Custom instruction profile

- See how long the simulator takes to execute each instruction

- Use to focus speed up simulation of instructions

- Enables improvement of speed of simulation runs

| sw                | 0.27s | 88,327,451  | 3.1ps/instruction (iss/c                               |

|-------------------|-------|-------------|--------------------------------------------------------|

| 1w                | 0.20s | 113,575,358 | 1.8ps/instruction (iss/c                               |

| mv .              | 0.16s | 134,497,608 | 1.2ps/instruction (iss/c                               |

| ret               | 0.07s | 16,843,028  | 4,2ps/instruction (iss/c                               |

| iel               | 0.06s | 16,843,026  | 3.6ps/instruction (iss/c                               |

| addi              | 0.05s | 58,868,837  | 0.8ps/instruction (iss/c                               |

| andi              | 0.05s | 33,620,233  | 1.5ps/instruction (iss/c                               |

| add               | 0.05e | 25,231,546  | 2.0ps/instruction (iss/c                               |

| auipc             | 0.04s | 4,210,858   | 9.5ps/instruction (iss/c                               |

| begz              | 0.03a | 29,426,103  | 1.0ps/instruction (iss/c                               |

| bnez              | 0,03s | 25,248,055  | 1.2ps/instruction (iss/c                               |

| chacha20gr3       | 0.03s | 8,388,608   | 3.6ps/instruction (iss/c                               |

| (JIT translation) | 0.03s | 2,500       | 12.0ns/instruction                                     |

| bltu              | 0.02s | 16,793,686  | 1.2ps/instruction (iss/c                               |

| chacha20gr1       | 0.02s | 8,388,608   | 2.4ps/instruction (iss/c                               |

| 1h                | 0.02s | 4,243,601   | 4.7ps/instruction (iss/c                               |

| xor               | 0.02s | 4,210,707   | 4.7ps/instruction (iss/c                               |

| slli              | 0.01s | 21,020,892  | 0.5ps/instruction (iss/c                               |

| srli              | 0.01s | 16,810,160  | 0.6ps/instruction (iss/c                               |

| bltz              | 0.01s | 8,421,470   | 1.2ps/instruction (iss/c                               |

| J                 | 0.01s | 8,388,742   | 1.2ps/instruction (iss/c                               |

| not               | 0.01s | 4,194,307   | 2.4ps/instruction (iss/c                               |

| (unallocated)     | 0.01s | 4,204,001   | 2. 4par Inscriaceton (1887 c)                          |

| bgeu              | 0.00s | 8,421,494   | 0.0ps/instruction (iss/c                               |

| chacha20gr2       | 0.00s | 8,388,608   | 0.0ps/instruction (iss/c                               |

| chacha20gr4       | 0.00s | 8,388,608   | 0.0ps/instruction (iss/c                               |

| sub               | 0.00s | 4,210,835   | 0.0ps/instruction (iss/c                               |

| beg               | 0.00s | 16,546      | 0.0ps/instruction (iss/c                               |

| jalr              | 0.00s | 16,430      | 0.0ps/instruction (iss/c                               |

| blez              | 0.00s | 16,407      | 0.0ps/instruction (iss/c                               |

| sb                | 0.00s | 206         | 0.0ps/instruction (iss/c                               |

| lhu               | 0.00s | 97          | 0.0ps/instruction (iss/c                               |

| sh                | 0.00s | 82          | 0.0ps/instruction (iss/c                               |

| lui               | 0.00s | 67          | 0.0ps/instruction (iss/c                               |

| or.               | 0.00s | 50          | 0.0ps/instruction (iss/c                               |

| and               | 0.00s | 49          | 0.0ps/instruction (iss/c                               |

| lbu               | 0.00s | 47          | 0.0ps/instruction (iss/c                               |

| bne               | 0.00s | 34          | 0.0ps/instruction (iss/c                               |

| ori               | 0,00s | 29          | 0.0ps/instruction (iss/c)<br>0.0ps/instruction (iss/c) |

|                   | 0.00s | 25          | 0.0ps/instruction (iss/c)                              |

| Jr<br>TOTAL       | 1,21s | 677,012,570 | O, Oper Instruction (1887c)                            |

#### Document custom instructions

- Imperas tools automatically generate a processor model document PDF

- Includes all base model registers and any new registers

- Provides detailed documentation of new custom instructions

#### Chapter 2

#### Instruction Extensions

RISCV processors may add various custom extensions to the basic RISC-V architecture. This processor has been extended, using an extension library, to add several instruction using the Custom0 opcode.

#### 2.1 Custom Instructions

This model includes four Chacha20 acceleration instructions (one for each rotate distance) are added to encode the XOR and ROTATE parts of the quarter rounds.

#### 2.1.1 chacha20qr1

| 31   | 25  | 24 | 20 | 19 | 1.5 | 14     | 12   | .11 | 7 | 6             | 0 |

|------|-----|----|----|----|-----|--------|------|-----|---|---------------|---|

| 0000 | 000 | Rs | 2  | Rs | 1   | 000 (0 | (R1) | Rd  |   | Custo<br>0001 |   |

#### 2.1.2 chacha20qr2

| 31   | 25  | 24 | 20 | 19  | 1.5 | 14     | 12  | 11 | 7 | 6                |  |

|------|-----|----|----|-----|-----|--------|-----|----|---|------------------|--|

| 0000 | 000 | Rs | 2  | Rsl |     | 001 (Q | R2) | Rd |   | Custon<br>000101 |  |

#### 2.1.3 chacha20qr3

| 31     | 25  | 24 | 20 | 19  | 15 | 14.    | 12   | 11 | 7 | 6                | - 1 |

|--------|-----|----|----|-----|----|--------|------|----|---|------------------|-----|

| . 0000 | 000 | Rs | 2  | Rsl |    | 010 (0 | QR3) | Rd |   | Custom<br>000101 |     |

# imperas

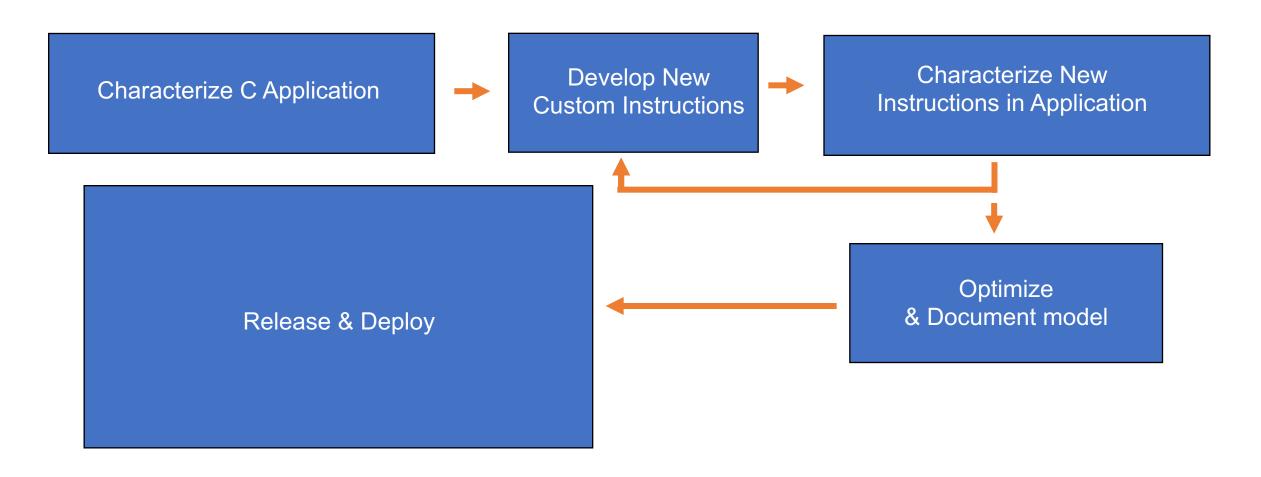

#### Characterize C Application

- Instruction Accurate Simulation

- Trace / Debug

- Timing Simulation

- Function Timing / Profiling

#### Develop New Custom Instructions

- Design Instructions

- Add to Application

- Add to Model

- Add Timing

#### Characterize New Instructions in Application

- Instruction Accurate Simulation

- Trace / Debug

- Timing Simulation

- Function Timing / Profiling

#### Release & Deploy

- Check RISC-V Compliance

- Use as reference for RTL Design Verification

- Use in Imperas/OVP Platforms, EPKs

- Heterogeneous / Homogeneous

- Multi-core, Many-core

- Imperas Multi-Processor Debug, VAP tools

- Port OS, RTOS (Linux, FreeRTOS...)

- Use in many simulation envs (inc. SystemC)

- Deliver to end users

#### Optimize & Document model

- Instruction Coverage

- Line Coverage

- Instruction Performance

- Generate PDF model doc

- Custom instructions are a key value proposition of RISC-V

- Adding custom instructions requires solving the key challenge of how to optimize those instructions

- Instruction accurate (IA) simulation environment using IA models can be extended to enable custom instruction analysis

- Flow for optimizing custom instructions in RISC-V processors is being used in real designs

#### Thank You

- For more information:

- LarryL@imperas.com

- Imperas website: <a href="http://www.imperas.com/riscv/">http://www.imperas.com/riscv/</a>

- Open Virtual Platforms (OVP): http://www.ovpworld.org/info\_riscv