RISC-V

### Commercially Supported RISC-V Simulation and Platform Development Tools

Simon Davidmann, Imperas Software Ltd.

© 2017 Imperas Software Ltd.

7th RISC-V Workshop, Nov. 2017

#### Who are Imperas?

- Leading independent commercial simulation vendor, established 10 years

- Solutions for small single core controller users all the way to high end 64bit MP Arm, MIPS architectural licensees

- Single licenses to enterprise wide regression farms

- Formed Open Virtual Platforms (OVP) to drive industry

- Oxford, UK HQ, Calif. US Sales, Distributors RoW

- Focus on embedded software development utilizing simulation

- models, simulators, tools, methodologies, solutions

## What we provide for Embedded Software Developer

- Fast Processor Models (200+) for different vendors/ISA (10+)

- High performance IA Simulator

- integrateable into 3rd party & test environments

- Tools for non-intrusive C Application profiling and line coverage

- GUI, Debugger multi-processor debugger

- Eclipse based, extended for hetero MP, programmers view

- Source code level, instruction, platform

- ISS and Extendable Platform Kits for flexibility and quick start

- Variety of extendable reference models of standard platforms running various operating systems (FreeRTOS, Linux, ...)

- Includes over 200 peripheral component models of standard parts (Ethernet, USB, CAN, ...) to easily create own platforms

- OS-aware tools for porting and bring up of operating systems, hypervisors, drivers

- Simulator designed to be used in regression test and Continuous Integration / Continuous Test environments

# What do we offer for RISC-V processor developers

- Commercially supported models, simulator, tools focused on RISC-V

- Highest performance RISC-V simulator: 25+ X faster than Spike

- All 32/64bit RISC-V CPU features implemented in simulator, currently 12 variant models, 6 vendor core models

- CPU models easily user extendable using standard tool features adding customer specific registers, instructions, behaviors

- CPU Model Code Coverage tool

- CPU Instruction Coverage tool

- CPU Cycle Approximate simulation using CPU cycle timing estimation

- CPU performance simulator interface e.g. to Gem5

- Interfaces for use with 3rd party simulators, RTL testbenches for DV

Imperas RISC-V processor verification tools/suite

OEM of Imperas commercially supported simulator and vendor specific models, platforms

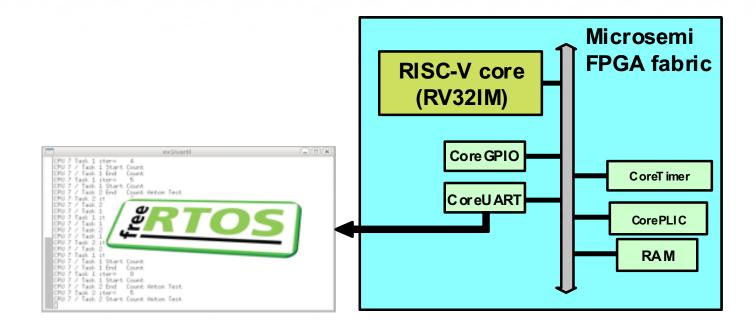

#### Imperas and Microsemi collaborate on RISC-V simulation models and tools

Mi-V Imperas FreeRTOS Extendable Platform Kit

#### Thank you!

## For more information about the leading commercial simulation, models, and tools for RISC-V designs:

www.imperas.com

www.OVPworld.org

Page 6

7th RISC-V Workshop, Nov. 2017